|

版主: 51FPGA |

如何连接待测试模块的内部信号到ILA观察?

[您是本帖的第5191位阅读者]|

becoll

最后登陆时间:2013-07-26 21:02:47 |

|

酒舞至尊。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

becoll

最后登陆时间:2013-07-26 21:02:47 |

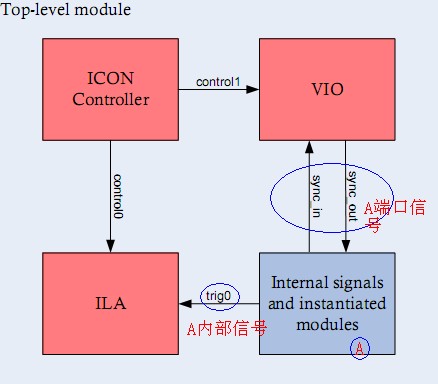

以前用chipscope都是用Core Inserter的方式插入chipscope核的,可以通过下图所示的图形界面直接连接待观察的内部信号,现在想用VIO核,而VIO核不支持Core Inserter的方式,所以只好用CORE Generator的方式了,而这种方式需要自己修改HDL代码建立连接关系,所以就不知道怎样去连接待观察的内部信号了,向用过该方式的高手求助!! |

酒舞至尊。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

Jason_Zhang

最后登陆时间:2015-01-20 09:30:43 |

你把ICO、VIO和ILA实例化到A模块中,至少我之前都是这么做的 |

My Email : zldpublic@gmail.com。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

becoll

最后登陆时间:2013-07-26 21:02:47 |

谢谢! 我没这么用过,所以有点怀疑。 假设A模块有个输入是复位信号——nRST,我想将它设为VIO,例化的VIO核中信号ASYNC_OUT和它对应,那么我的A文件中应该添加如下语句: nRST<=ASYNC_OUT; (VHDL)或 assign nRST=ASYNC_OUT; (Verilog) 而nRST本身就是A模块的输入信号,所以我感觉在A模块中加上上面的语句有点不合适 我先试试看有没有问题吧,谢谢解答~ |

酒舞至尊。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

Jason_Zhang

最后登陆时间:2015-01-20 09:30:43 |

becoll的原帖 谢谢! 我没这么用过,所以有点怀疑。 假设A模块有个输入是复位信号——nRST,我想将它设为VIO,例化的VIO核中信号ASYNC_OUT和它对应,那么我的A文件中应该添加如下语句: nRST<=ASYNC_OUT; (VHDL)或 assign nRST=ASYNC_OUT; (Verilog) 而nRST本身就是A模块的输入信号,所以我感觉在A模块中加上上面的语句有点不合适 我先试试看有没有问题吧,谢谢解答~ VIO我没用过。 这样的话,就要把nRst先从端口去了才行吧 |

My Email : zldpublic@gmail.com。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

becoll

最后登陆时间:2013-07-26 21:02:47 |

becoll的原帖 Jason_Zhang的原帖谢谢! 我没这么用过,所以有点怀疑。 假设A模块有个输入是复位信号——nRST,我想将它设为VIO,例化的VIO核中信号ASYNC_OUT和它对应,那么我的A文件中应该添加如下语句: nRST<=ASYNC_OUT; (VHDL)或 assign nRST=ASYNC_OUT; (Verilog) 而nRST本身就是A模块的输入信号,所以我感觉在A模块中加上上面的语句有点不合适 我先试试看有没有问题吧,谢谢解答~ VIO我没用过。 这样的话,就要把nRst先从端口去了才行吧 这样子确实可以,谢谢! 还想请教一下:用这种core generator的方式如何将ila中信号的重命名、进制显示方式等设置保存下来啊?每次重新设置挺麻烦的,没发现怎样存cdc文件,不知怎样操作? |

酒舞至尊。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

Jason_Zhang

最后登陆时间:2015-01-20 09:30:43 |

在Analizer中可以直接保存啊 |

My Email : zldpublic@gmail.com。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

becoll

最后登陆时间:2013-07-26 21:02:47 |

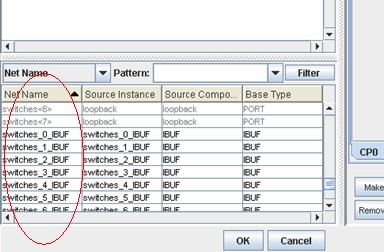

不太明白,你是指下图所示的窗口吗? 用core insertor 方式使用chipscope时会自动产生一个cdc文件,使用analyser时直接将这个cdc文件import进来就行了,不知道你所说的直接存是存一个什么文件?是工程文件.prj么还是上图中所示的某种文件? 谢谢! |

酒舞至尊。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

Jason_Zhang

最后登陆时间:2015-01-20 09:30:43 |

在ChipScope Pro Analyzer中,File ---> save,保存为cpj格式就可以了 |

My Email : zldpublic@gmail.com。 |

|

RE: 如何连接待测试模块的内部信号到ILA观察?

|

becoll

最后登陆时间:2013-07-26 21:02:47 |

多谢啊!受核插入法的影响,头脑没转过弯来,呵呵! |

酒舞至尊。 |

|

Xilinx

Xilinx