1#

发表于 2015-07-25 23:48:31

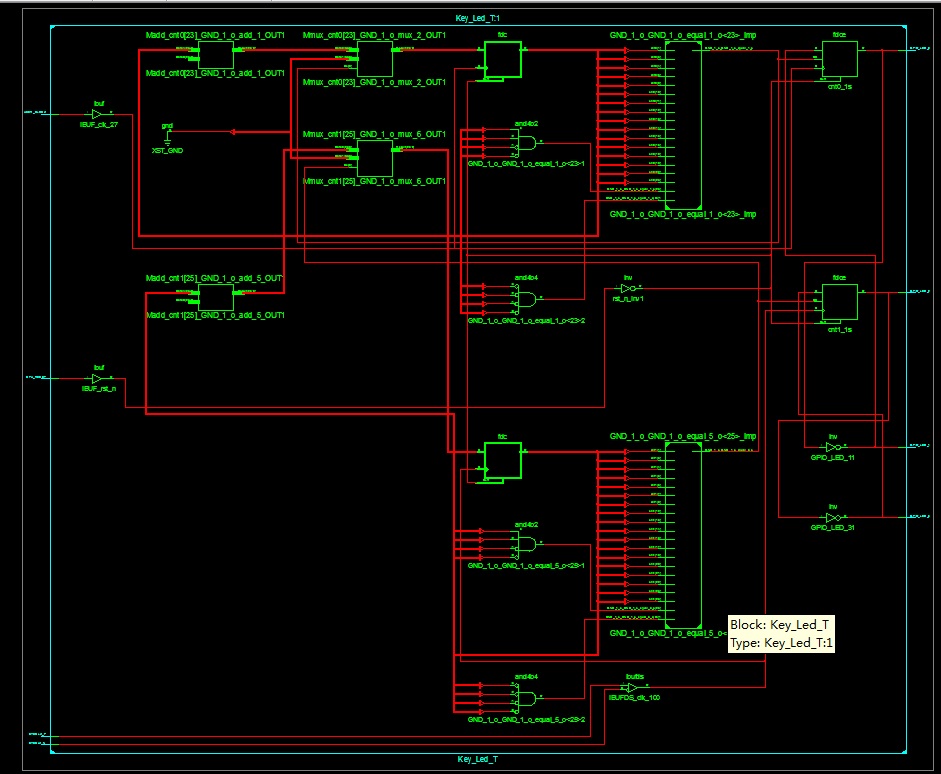

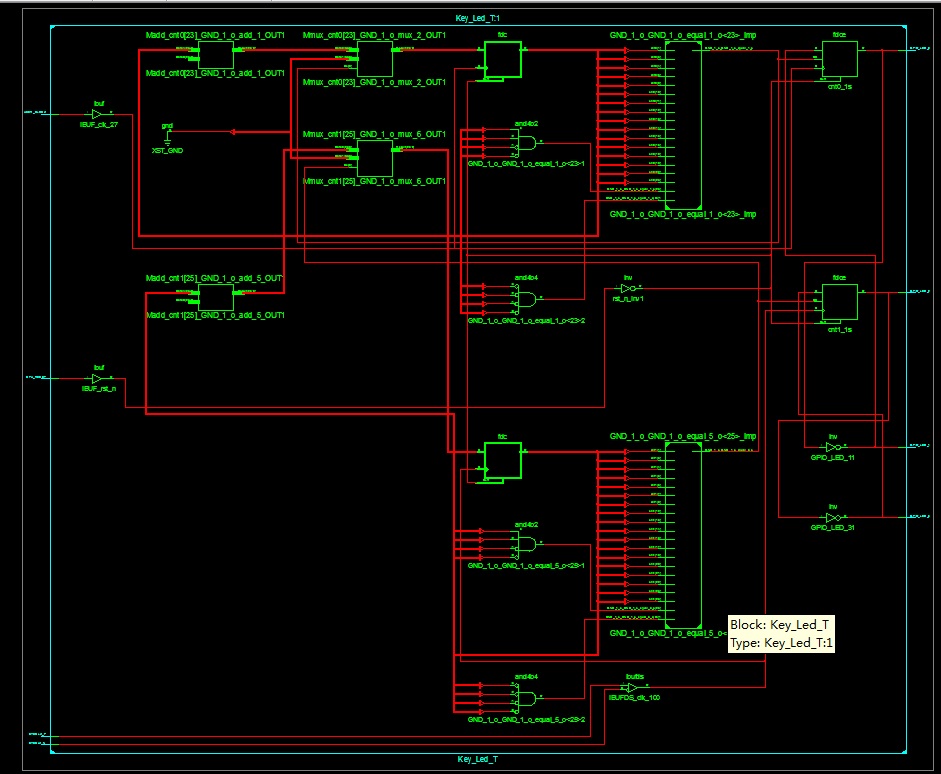

ISE 14.7 下面代码会在CPU RESET的输入端综合出反相器来,怎么回避这个问题?

module Key_Led_T(

CPU_RESET,USER_CLOCK,

GPIO_LED_0,GPIO_LED_1,GPIO_LED_2,GPIO_LED_3

);

input CPU_RESET , USER_CLOCK;

output GPIO_LED_0,GPIO_LED_1,GPIO_LED_2,GPIO_LED_3;

//--------------------------------------------------------------------------------------------1

(* KEEP ="TRUE" *) wire rst_n;

IBUF #(

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

)IBUF_rst_n(

.O(rst_n), // Buffer output

.I(CPU_RESET) // Buffer input (connect directly to top-level port)

);

//--------------------------------------------------------------------------------------------2

wire clk_27;

IBUF #(

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

)IBUF_clk_27 (

.O(clk_27), // Buffer output

.I(USER_CLOCK) // Buffer input (connect directly to top-level port)

);

parameter CLK_FREQUENCY1 = 27000000;

reg[23:0] cnt0;

reg cnt0_1s;

always@(posedge clk_27 or negedge rst_n)begin

if(!rst_n)begin

cnt0 <= 0;

cnt0_1s <= 0;

end

else if(cnt0 == (CLK_FREQUENCY1/2) - 1)begin

cnt0 <= 0;

cnt0_1s <= ~cnt0_1s;

end

else begin

cnt0 <= cnt0 + 1;

end

end

assign GPIO_LED_0 = cnt0_1s;

assign GPIO_LED_1 = ~cnt0_1s;

assign GPIO_LED_2 = cnt0_1s;

assign GPIO_LED_3 = ~cnt0_1s;

|

Xilinx

Xilinx