1#

发表于 2015-07-30 22:55:40

1、什么是AXI

AXI(Advanced eXtensible Interface)是一种总协议,该协议的第一个版本AXI3是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分。2010发布的AMBA4.0包含了AXI的第二个版本AXI4。

AXI4包含3种类型的接口:

1)AXI4:主要面向高性能地址映射通信的需求;

2)AXI4-Lite:是一个轻量级的,适用于吞吐量较小的地址映射通信总线;

3)AXI4-Stream:面向高速流数据传输。

2、AXI4协议的优势

1)高效:通过标准化的AXI接口,开发者只需要学习一种IP核的通讯协议即可;

2)易用:针对具体应用提供合适的接口协议。

AXI4:面向地址映射的接口,在单地址传输的情况下最大允许256个时钟周期的数据突发长度;

AXI4-Lite:一个轻量级的地址映射单次传输接口,占用较少的资源;

AXI4-Stream:去掉了地址传输的功能,允许无限制的数据突发传输,无需考虑地址映射。

3)易得:标准化的AXI接口协议资源,不仅可以在xilinx官网上获得,也可以在全球范围内ARM的所有合作伙伴处获得。

大量的IP core支持AXI4协议;

大量的第三方AXI工具可提供多样的系统开发、验证和功能定制。

3、AXI4的工作模式

AXI4和AXI4-Lite包含5个不同的通道:

读地址通道

写地址通道

读数据通道

写数据通道

读响应通道

数据可以在主从设备间同步的双向传输,并且数据传输大小可以改变。AXI4将数据传输的突发长度限制为最大256,AXI4-Lite每次传输仅运输传输一个数据。

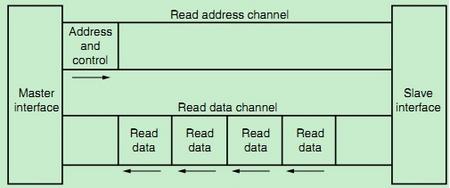

如图1所示,AXI4协议主从设备间的读操作使用独立的读地址和读数据通道,只需要一个地址就可以执行最大为256的突发长度的读操作。

图1 读操作的通道结构

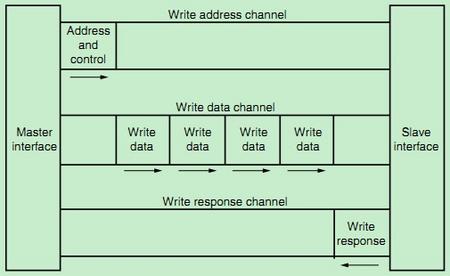

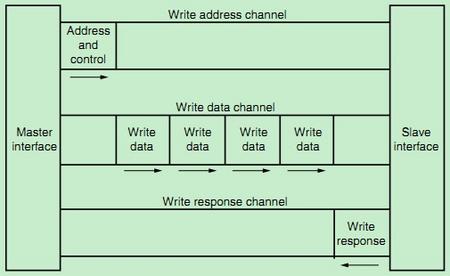

如图2所示,AXI4协议主从设备间的写操作使用写地址、写数据和写响应通道。只需要一个地址就可以执行最大为256的突发长度的写操作。

图2写操作的通道结构

AXI4-Lite接口和AXI4接口类似,但是不支持AXI4的突发传输模式。AXI4-Stream接口仅使用数据通道传输数据流,数据突发长度无限。

4、AXI4和AXI4-Lite接口信号

1)全局信号

|

信号名

|

AXI4

|

AXI4-Lit

|

|

ACLK

|

全局时钟

|

|

ARESETN

|

全局复位,低有效。

|

2)写地址通道信号

|

信号名

|

源

|

AXI4

|

AXI4-Lit

|

|

AWID

|

主

|

写地址ID。这个信号用于写地址信号组的标记。

|

不支持

|

|

AWADDR

|

主

|

写地址。写地址给出突发数据传输的第一个传输地址。

|

|

AWLEN

|

主

|

突发长度。给出突发传输中准确的传输个数。支持INCR和WRAP传输模式。

|

不支持

|

|

AWSIZE

|

主

|

突发大小。这个信号用于确定突发传输中每个传输的大小。

|

不支持

|

|

AWBURST

|

主

|

突发类型。该信息与突发大小信息一起,表示在突发过程中,地址如何应用于每个传输。支持INCR和WRAP传输模式。

|

不支持

|

|

AWLOCK

|

主

|

锁类型。该信号提供了关于传输原子特性的额外信息(普通或互斥访问)。

|

不支持

|

|

AWCACHE

|

主

|

缓存类型,建议值为0011。

|

|

AWPROT

|

主

|

保护类型,建议值为000。

|

|

AWQOS

|

主

|

QoS标识符,xilinx AXI4不支持。

|

不支持

|

|

AWREGION

|

主

|

用于每个写操作的地址通道上的域标识符。

|

不支持

|

|

AWUSER

|

主

|

xilinx AXI4不支持。

|

不支持

|

|

AWVALID

|

主

|

写地址有效信号。为高指示地址有效。

|

|

AWREADY

|

从

|

写地址准备信号。为高表示从设备空闲,准备接收地址;为低表示从设备忙。

|

3)写数据通道信号

|

信号名

|

源

|

AXI4

|

AXI-Lite

|

|

WDATA

|

主

|

写数据,32位到1024位宽

|

只支持32位宽

|

|

WSTRB

|

主

|

写字节选通,用于表示更新存储器的字节通道,对于数据总线的每8位数据有一位写选通信号。

|

从设备端可选择忽略。

|

|

WLAST

|

主

|

写最后一个数据指示信号。表示突发传输中的最后一个数据。

|

不支持

|

|

WUSER

|

主

|

xilinx AXI4不支持。

|

不支持

|

|

WVALID

|

主

|

写有效。为高指示数据有效。

|

|

WREADY

|

从

|

写准备。为高表示从设备空闲,准备接收数据;为低表示从设备忙。

|

4)写响应通道

|

信号名

|

源

|

AXI4

|

AXI-Lite

|

|

BID

|

从

|

响应ID。写响应识别标记,BID值必须匹配AWID值。

|

不支持

|

|

BRESP

|

从

|

写响应。该信号表示写状态,可允许相应的表示为OKAY\EXOKAY\SLVERR\DECERR。

|

EXOKAY状态不支持

|

|

BUSER

|

从

|

xilinx AXI4不支持。

|

不支持

|

|

BVALID

|

从

|

写响应有效。为高指示响应数据有效。

|

|

BREADY

|

主

|

写响应准备。为高表示主设备空闲,准备接收写响应;为低表示主设备忙。

|

5)读地址通道

|

信号名

|

源

|

AXI4

|

AXI-Lite

|

|

ARID

|

主

|

读地址ID。这个信号用于读地址信号组的标记。

|

不支持

|

|

ARADDR

|

主

|

读地址。读地址给出突发数据传输的第一个传输地址。

|

|

ARLEN

|

主

|

突发长度。给出突发传输中准确的传输个数。支持INCR和WRAP传输模式。

|

不支持

|

|

ARSIZE

|

主

|

突发大小。这个信号用于确定突发传输中每个传输的大小。

|

不支持

|

|

ARBURST

|

主

|

突发类型。该信息与突发大小信息一起,表示在突发过程中,地址如何应用于每个传输。支持INCR和WRAP传输模式。

|

不支持

|

|

ARLOCK

|

主

|

锁类型。该信号提供了关于传输原子特性的额外信息(普通或互斥访问)。

|

不支持

|

|

ARCACHE

|

主

|

缓存类型,建议值为0011。

|

|

ARPROT

|

主

|

保护类型,建议值为000。

|

|

ARQOS

|

主

|

QoS标识符,xilinx AXI4不支持。

|

不支持

|

|

ARREGION

|

主

|

用于每个读操作的地址通道上的域标识符。

|

不支持

|

|

ARUSER

|

主

|

xilinx AXI4不支持。

|

不支持

|

|

ARVALID

|

主

|

读地址有效信号。为高指示地址有效。

|

|

ARREADY

|

从

|

读地址准备信号。为高表示从设备空闲,准备接收地址;为低表示从设备忙。

|

6)读数据通道

|

信号名

|

源

|

AXI4

|

AXI-Lite

|

|

RID

|

从

|

读ID标记,该信号是读数据信号组标记,由从设备产生RID,RID必须和读交易中的ARID匹配。

|

不支持

|

|

RDATA

|

从

|

读数据。32位到1024位宽

|

只支持32位宽

|

|

RRESP

|

从

|

读响应。该信号表示读状态,可允许相应的表示为OKAY\EXOKAY\SLVERR\DECERR。

|

EXOKAY状态不支持

|

|

RLAST

|

从

|

读最后一个数据指示信号。表示突发传输中的最后一个数据。

|

不支持

|

|

RUSER

|

从

|

xilinx AXI4不支持。

|

不支持

|

|

RVALID

|

从

|

读有效。为高指示数据有效。

|

|

RREADY

|

主

|

读准备。为高表示主设备空闲,准备接收数据;为低表示主设备忙。

|

7)AXI4-Stream信号

|

信号名

|

源

|

默认值

|

功能

|

|

TVALID

|

No

|

N/A

|

Stream读写数据有效。为高指示数据有效。

|

|

TREADY

|

Yes

|

1

|

Stream读写读准备。为高表示对端设备空闲,准备接收数据;为低表示对端设备忙。

|

|

TDATA

|

Yes

|

0

|

Stream读写数据,8到4096位宽。

|

|

TSTRB

|

Yes

|

同TKEEP,否则为1

|

字节选通信号。用于表示更新存储器的字节通道,对于数据总线的每8位数据有一位选通信号。

|

|

TKEEP

|

Yes

|

1

|

字节选通信号。TKEEP未被确认的那些相关的字节是空字节,可以从数据流中去除。

|

|

TLAST

|

Yes

|

0

|

表明包的边界。

|

|

TID

|

Yes

|

0

|

数据流标识符。

|

|

TDEST

|

Yes

|

0

|

数据流路由信息。

|

|

TUSER

|

Yes

|

0

|

用户定义的边带信息,这些信息能伴随数据流进行发送。

|

|

Xilinx

Xilinx