|

版主: 51FPGA |

VGA显示系统设计

[您是本帖的第3850位阅读者]|

zhaobingpo

最后登陆时间:2014-07-30 15:01:01 |

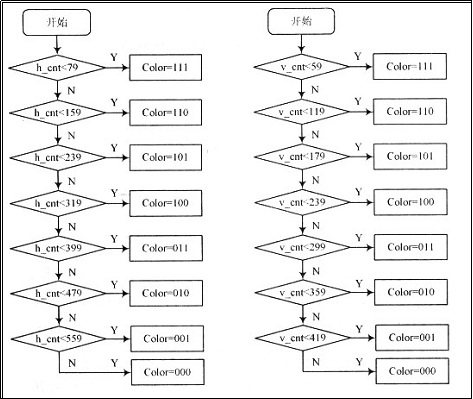

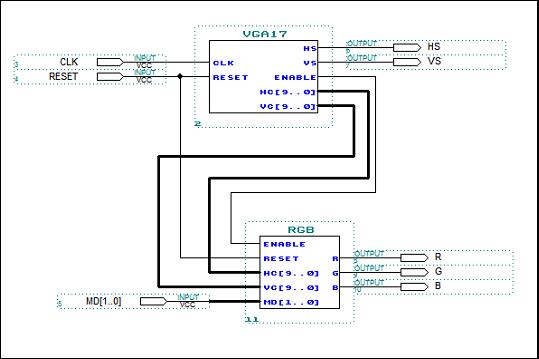

一.实验目的: 1、根据VGA视频信号时序,利用FPGA控制产生视频信号,在普通彩色显示器上显示8色彩色图像。 2、在显示器上显示自行设计的彩色规则图形——棋盘形。 二.实验原理: 1概述 该系统实现的目标是将数据源写入视频存储器中的视频数据通过D/A转换器输出给VGA显示器,从而得到预期的视频显示。按照这个目的,FPGA作为整个设计的核心,负责产生正确的行同步信号和场同步信号输出给VGA显示器,使VGA显示器能够正确的同步:负责进行水平、垂直计数,并将计数器的值或行、场同步信号转换成存储器的地址数据输出给视频存储阵列,使视频存储阵列能够正确的输出图像的颜色信息:负责根据同步时序控制D/A转换器及时的把视频存储阵列输出的颜色的数字量转换成模拟量送给VGA显示器。 FPGA是整个系统的中枢,在FPGA内部,主要有两个模块:一个是时序生成模块,另一个是地址产生模块。它根据外部时钟CLK进行计数,并根据计数器的值来确定行、场所处的位置,并依此产生以下信号:行同步信号(Hs),场同步信号(Vs),地址信号,和输出允许信号。其中,行同步信号和场同步信号是严格的周期信号,直接送给通过VGA接口相连的VGA显示器做同步使用。只要连接这两个信号就完全可以点亮显示器,只不过在显示器上没有任何的颜色信息。输入允许段一共有两个,一个是视频存储阵列的输出允许端,它控制视频存储阵列锁存地址线上的地址对应单元的数据。另外一个输出允许端是控制D/A转换阵列的。 视频存储阵列是由三块容量和参数一样的双口RAM堆叠而成,三块RAM是独立的并列关系。它们每一块负责存储三原色中一种颜色的数字量。三块RAM分别存储红(R),绿(G),蓝(B)分量。双口RAM输入端的地址和数据全部来自CPU或外部的数据采集源,输出端的地址由FPGA产生,而数据则直接输出给视频D/A转换阵列。 CLK引脚是整个系统需要的唯一的外部时钟,设计要求它能够提供50MHz的时钟频率,FPGA内部进行二分频后使用。RESET是整个系统的复位端。最后是整个系统的输出与VGA接口的连接。将行同步信号(Hs)与VGA接口的13脚连接,场同步信号(Vs)与14脚相连,D/A转换阵列的R分量与1脚连接,G分量与2脚,B分量与3脚连接就可以完成整个系统的连接工作。 时序产生模块: 时序产生的目的是根据外部时钟进行水平和垂直计数,并根据计数值进行判断,若此时在消隐区,需要把ShZone设为低电平。并要判断是否是同步时间,若是,则在行同步或场同步信号上输出同步脉冲。 时序产生模块主要有水平计数器和垂直计数器。水平计数器的计数脉冲是外部时钟CLK,而垂直计数器的计数脉冲是行同步信号Hs的同步头。这个模块的输入时钟是25MHz的时钟频率,输出端是行同步信号(Hs)、场同步信号(Vs)、水平计数器(Hcnt)、垂直计数器(Vcnt)、和有效显示信号(ShZone)5个信号。其中,Hs、Vs直接送给VGA显示器,Hcnt、Vcnt、ShZone则输出给地址产生模块。 一个行周期含有800个像素时钟,在时序产生模块中定义如下: constant H_PIX : INTEGER:=640;----行数据区 行计数器是一个10比特的向量信号,定义如下: signal hcnt: std_logic_vector(9 downto 0); 根据水平计数器的值决定了行同步信号(Hs)和有效显示信号(ShZone)。 Hs信号变化如下: if (hcnt >= (H_PIX + H_FRONT) and hcnt < (H_PIX + H_SYNC + H_FRONT)) then ShZone信号变化如下: if hcnt >= H_PIX or vcnt >= V_LINES then 彩条产生模块 竖彩条发生模块流程图 横彩条发生模块流程图 2实验原理图: 1)彩条发生电路原理图(时序控制模块+彩条产生模块)

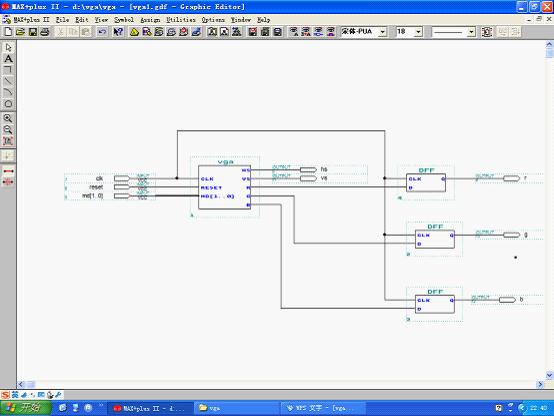

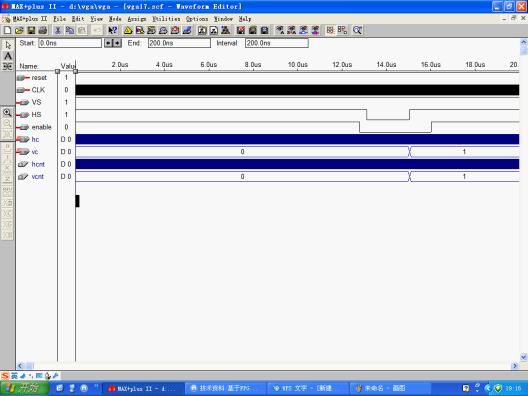

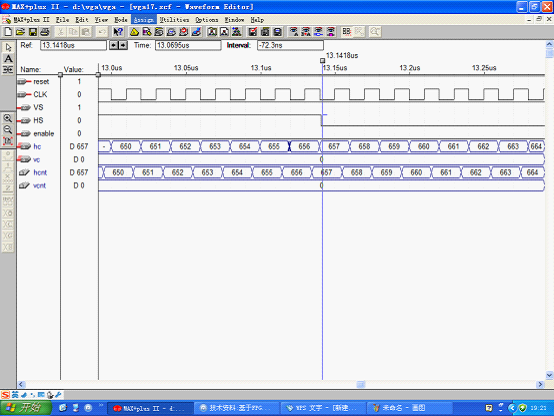

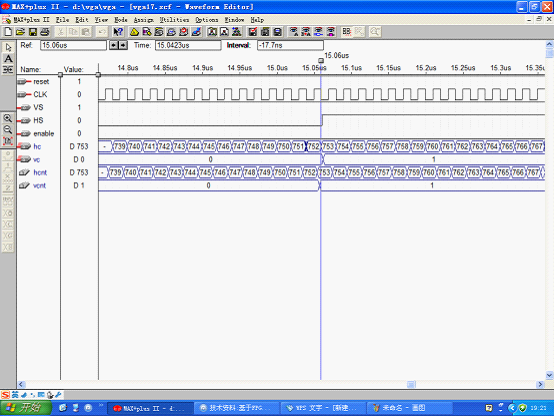

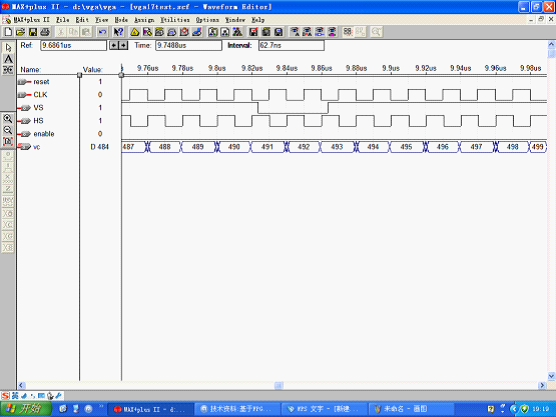

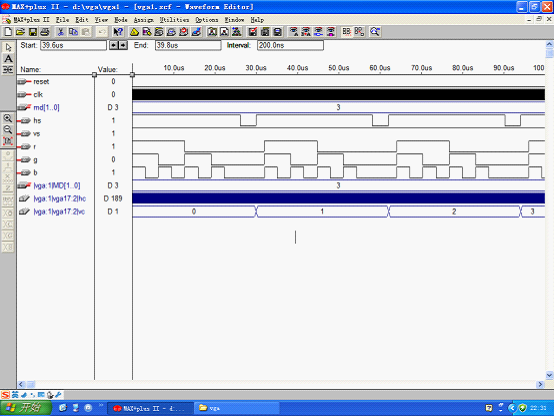

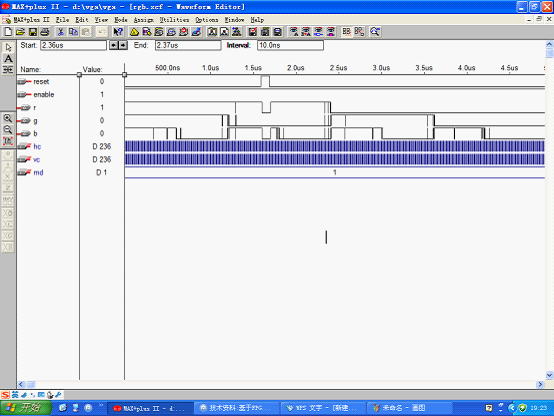

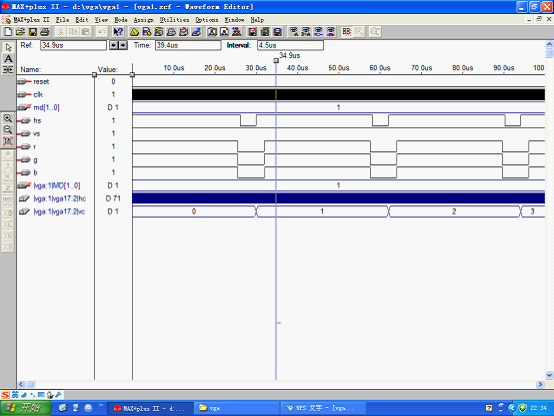

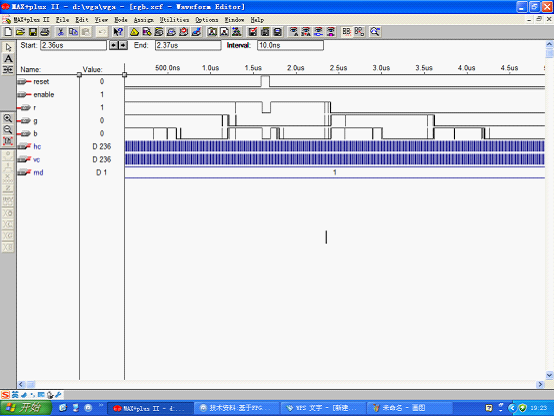

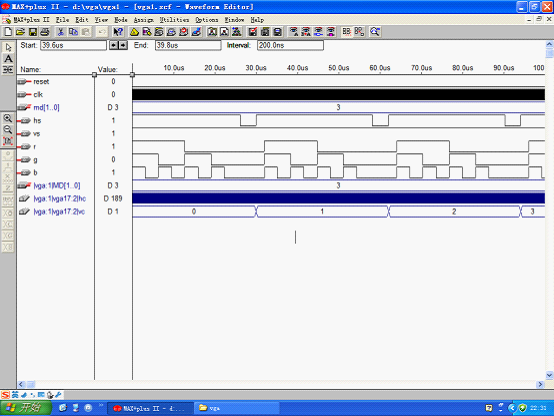

3vhdl文件 1)时序控制模块vhdl文件 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY vga17 IS PORT ( CLK,reset: IN STD_LOGIC; HS:buffer std_logic; VS,enable: OUT STD_LOGIC ; hc,vc: out std_logic_vector(9 downto 0)); END vga17; ARCHITECTURE behav OF vga17 IS SIGNAL HS1,VS1,enable1,hclk,vclk: STD_LOGIC; SIGNAL hcnt: STD_LOGIC_VECTOR(9 DOWNTO 0); SIGNAL vcnt: STD_LOGIC_VECTOR(9 DOWNTO 0); Constant H_PIX :INTEGER:=640; Constant H_FRONT :INTEGER:=16; Constant H_BACK :INTEGER:=48; Constant H_SYNC :INTEGER:=96; Constant H_TIME:INTEGER:=H_PIX+H_FRONT+H_BACK+H_SYNC; constant V_pix: integer:=480; constant v_front:integer:=10; constant v_sync:integer:=2; constant v_back:integer:=33; constant v_time:integer:=v_pix+v_front+v_sync+v_back; begin PROCESS( CLK ,reset) BEGIN if (reset='0') then hcnt <= "0000000000"; elsIF (CLK'EVENT AND CLK = '1') THEN IF (hcnt <H_TIME) THEN hcnt <= hcnt+1; ELSE hcnt <= "0000000000"; END IF; END IF; END PROCESS; process(HS,reset) BEGIN if (reset='0') then vcnt <= "0000000000"; elsIF (hs'EVENT AND hs = '1') THEN IF (vcnt < v_time) THEN vcnt <= vcnt + 1; ELSE vcnt <= "0000000000"; END IF; END IF; END PROCESS; process(clk,reset) begin if reset='0' then hs<='1'; elsif (clk'event and clk='1') then if (hcnt>=(h_PIX+h_FRONT) and hcnt< (h_PIX+h_SYNC+h_FRONT)) then hs<='0'; else hs<='1'; end if; end if; end process; process(hs,reset) begin if reset='0' then vs<='1'; elsif(hs'event and hs='1') then if (vcnt>=(v_PIX+v_FRONT) and vcnt< (v_PIX+v_SYNC+v_FRONT)) then vs<='0'; else vs<='1'; end if; end if; end process; process(clk) begin if clk'event and clk='1' then if hcnt>=h_pix or vcnt>=v_pix then enable<='0'; else enable<='1'; end if; end if; end process; hc<=hcnt;vc<=vcnt; end ARCHITECTURE behav; 2)彩条产生模块vhdl文件 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY rgb IS PORT ( enable,reset:in std_logic; hc,vc: IN STD_LOGIC_vector(9 downto 0); md: in std_logic_vector(1 downto 0); r,g,b: OUT STD_LOGIC ); END rgb; ARCHITECTURE behav OF rgb IS signal rgbx,rgby,rgb: std_logic_vector(2 downto 0); begin process (md,enable,reset) begin if reset='1' then rgb<="000"; elsif enable='1'then if md="11" then rgb <= rgbx; elsif md="01" then rgb <=rgby; elsif md="10" then rgb <=rgbx xor rgby; else rgb <="000"; end if; else rgb <="000"; end if; end process; process(hc) begin if hc <79 then rgbx<="111"; elsif hc<159 then rgbx<="110"; elsif hc<239 then rgbx<="101"; elsif hc<319 then rgbx<="100"; elsif hc<399 then rgbx<="011"; elsif hc<479 then rgbx<="010"; elsif hc<559 then rgbx<="001"; else rgbx<="000"; end if; end process; process(vc) begin if vc <59 then rgby<="111"; elsif vc<119 then rgby<="110"; elsif vc<179 then rgby<="101"; elsif vc<239 then rgby<="100"; elsif vc<299 then rgby<="011"; elsif vc<359 then rgby<="010"; elsif vc<419 then rgby<="001"; else rgby<="000"; end if; end process; r<=rgb(2);g<=rgb(1);b<=rgb(0); end ARCHITECTURE behav; 3)D触发器模块vhdl文件 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY dff IS PORT ( CLK: IN STD_LOGIC; D:in std_logic; Q: OUT STD_LOGIC ); END dff; ARCHITECTURE behav OF dff IS begin process(clk) begin if clk'event and clk='1'then q<=d; end if; end process; end architecture behav; 三.仿真波形 1.行同步

2.场同步信号

3.竖彩条

4.横彩条

5.D触发器去毛刺

不加D触发器时的波形

加D触发器后的波形 关键词:显示系统 设计 视频 信号 产生 显示器 输出 同 |

赵兵坡。 |

|

RE: VGA显示系统设计

|

Jason_Zhang

最后登陆时间:2015-01-20 09:30:43 |

不错的东西,很详细。感谢楼主分享 |

My Email : zldpublic@gmail.com。 |

|

RE: VGA显示系统设计

|

dreamjsc

最后登陆时间:2012-06-04 16:42:28 |

不错,很详细 |

大山里的娃儿。 |

|

RE: VGA显示系统设计

|

Ottomia

最后登陆时间:2014-04-12 21:52:33 |

楼主有么有做过VGA字符显示的啊?或是图像显示的

|

学习知识。 |

|

| 共5条 1/1 1 |

Xilinx

Xilinx