|

版主: 51FPGA |

合仿真疑惑

[您是本帖的第2204位阅读者]|

hardyyang

最后登陆时间:2014-11-18 14:21:22 |

各位朋友大家好,小弟正自学CPLD。 关键词:仿真 疑惑 |

无知者无过。 |

|

RE: 合仿真疑惑

|

hardyyang

最后登陆时间:2014-11-18 14:21:22 |

我采用的是XC9500 CPLDs,我改为virtex XCV200使用syc clr_in看到综合底层的元件是OK的,请问是什么原因呢? |

无知者无过。 |

|

RE: 合仿真疑惑

|

jackwang

最后登陆时间:2015-01-29 08:45:11 |

jasonzhang近日很忙,一般的FPGA他全都能搞定

|

http://t.sina.com.cn/eepw。 |

|

RE: 合仿真疑惑

|

Jason_Zhang

最后登陆时间:2015-01-20 09:30:43 |

能把你综合后的RTL贴上来看看吗? |

My Email : zldpublic@gmail.com。 |

|

RE: 合仿真疑惑

|

hardyyang

最后登陆时间:2014-11-18 14:21:22 |

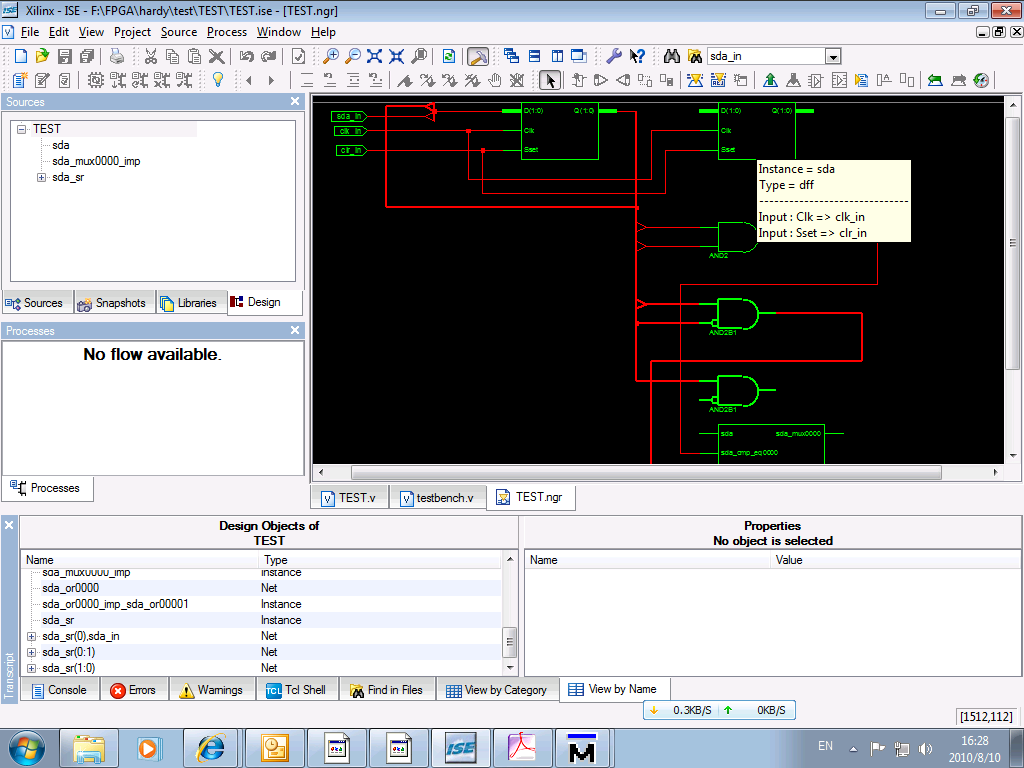

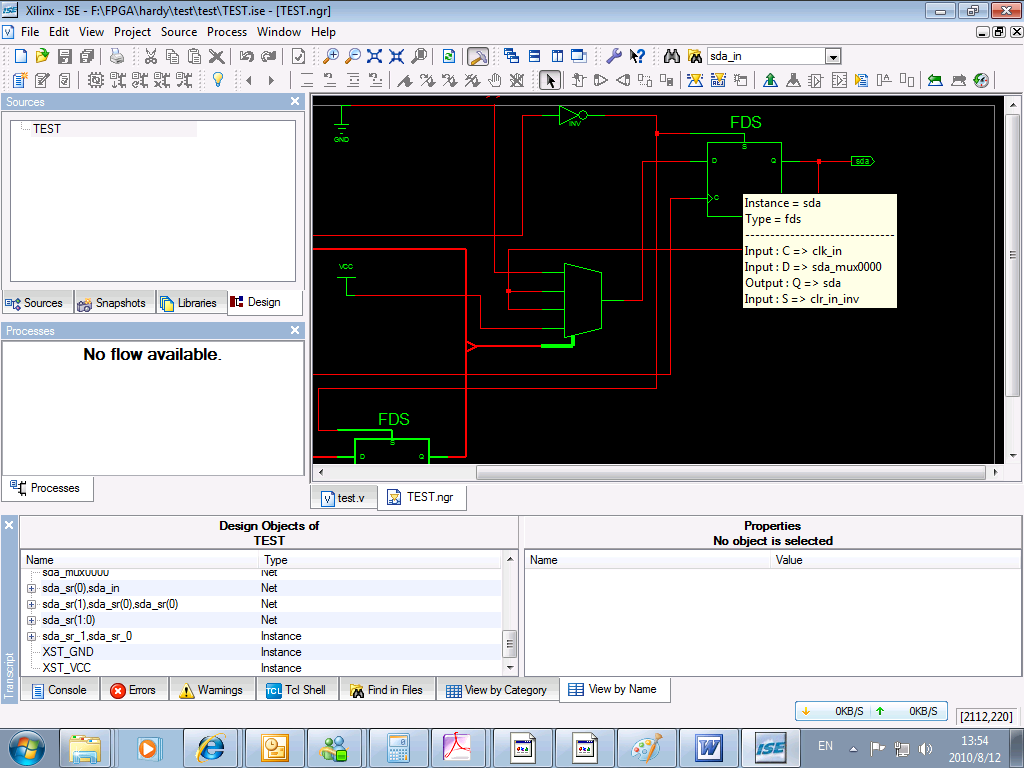

Hi,Jashon, 图片我已上传了。上面那幅图片是使用XC9500 CPLD综合的结果,而下面这幅图是使用Virtek综合的结果,从图中可看出sda一个没有引出,而另一个有引出。

非常感谢!  |

无知者无过。 |

|

RE: 合仿真疑惑

|

jiangnanyu

最后登陆时间:2010-08-26 09:42:30 |

DDDDDDDDDDDD

|

| 共7条 1/1 1 |

Xilinx

Xilinx