|

版主: 51FPGA |

MPSOC学习之HELLO WORLD

[您是本帖的第1428位阅读者]|

myyangyang

最后登陆时间:2019-07-23 15:18:43 |

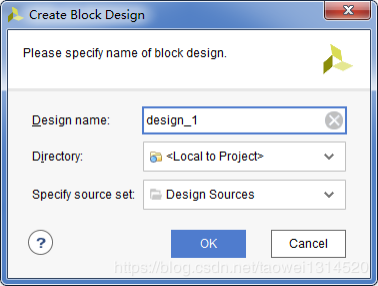

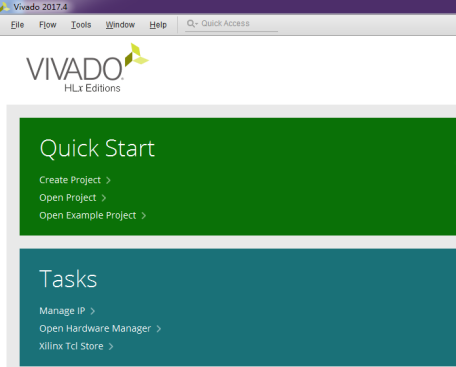

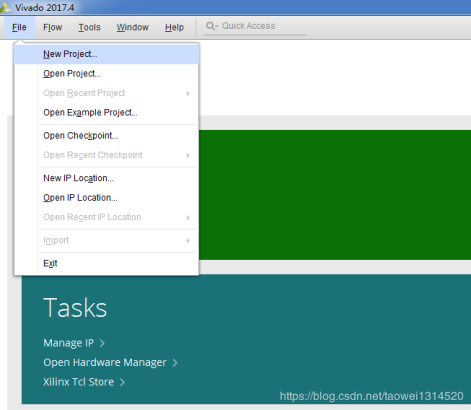

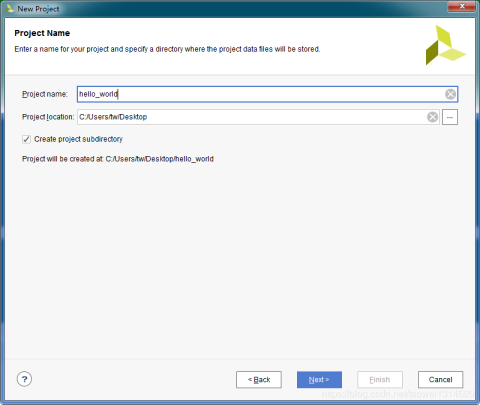

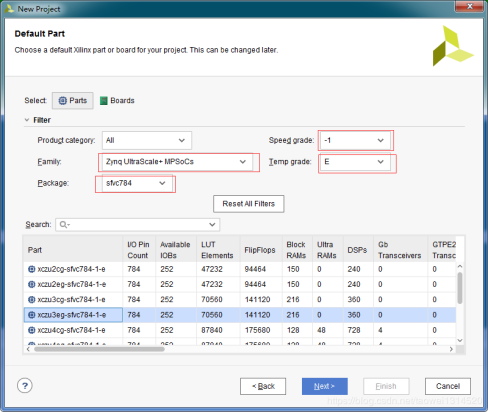

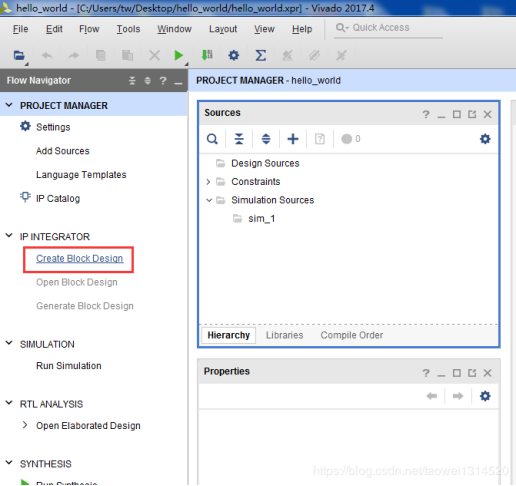

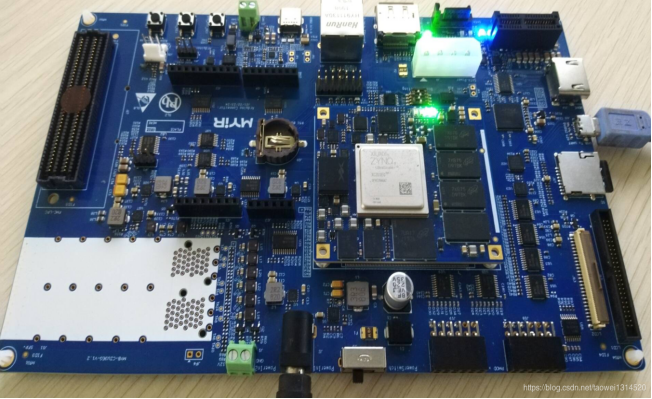

早就听闻XILINX 新一代 SOC,Zynq UltraScale+ MPSOC 系列性能强悍无比,号称相比ZYNQ 7000系列每瓦性能提升5倍,一直未能体验一把。直到近期因项目需要,入手了一套米尔的MPSOC开发板,才终于开启了MPSOC学习之路。废话不说,hello world先。 开发环境:vivado 2017.4,开发板型号:米尔MYD-CZU3EG, 主芯片XCZU3EG-1SFVC784。这个系列板子还有4EV,5EV等版本,手里的3EG版本不支持SFP,因此板上相应接口(白色部分)是空贴的。  Step1 新建vivado工程 打开vivado 2017.4  选择File-->New Project  点击Next 填写工程名和选择工程保存路径,点击Next  点击Next, 按照截图的配置选择开发板型号为 xczu3eg-sfvc784-1-e ,点击Next  点击Finish,新建的vivado工程,如下图所示  Step2 新建Block Design 点击导航栏的Create Block Design  这里可以自己填写名称,我这里直接用默认的名称,点击OK

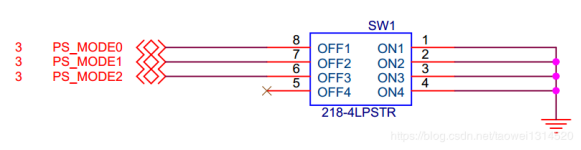

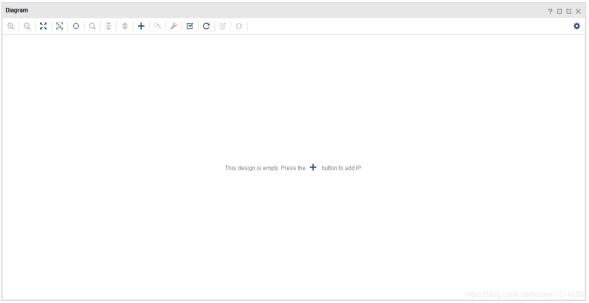

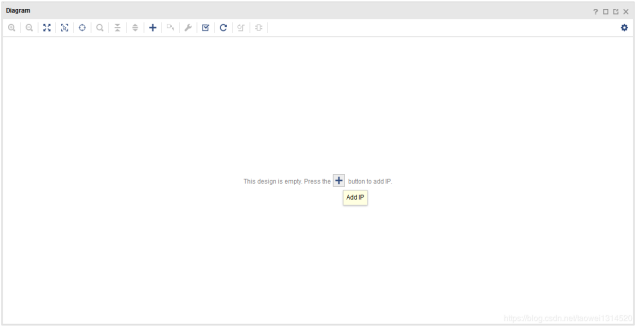

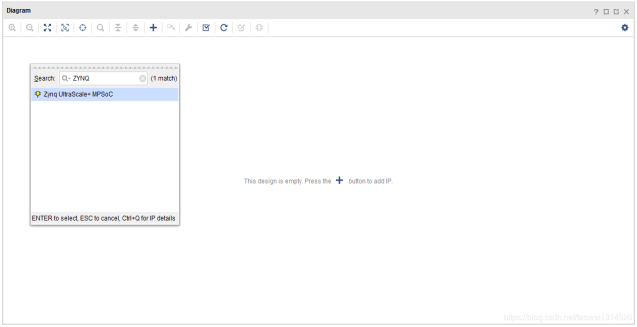

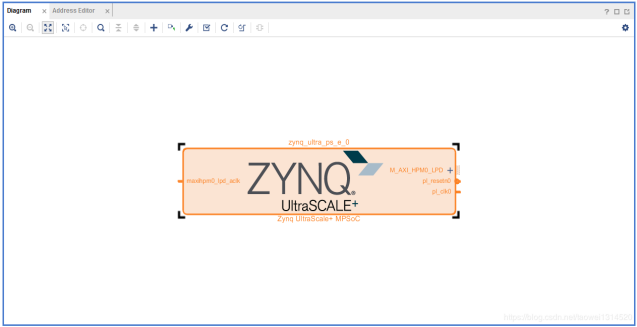

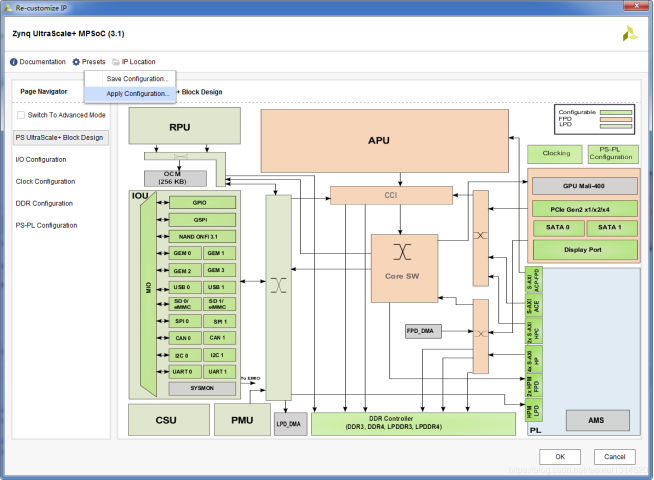

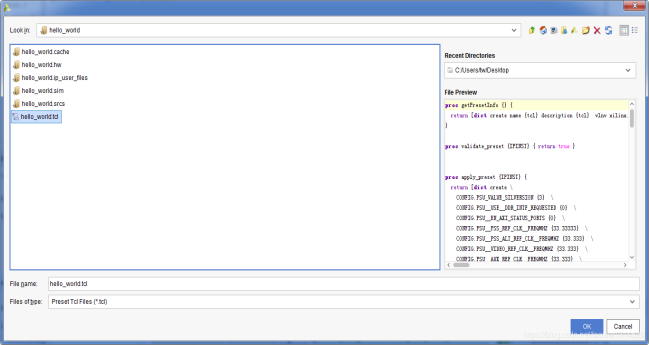

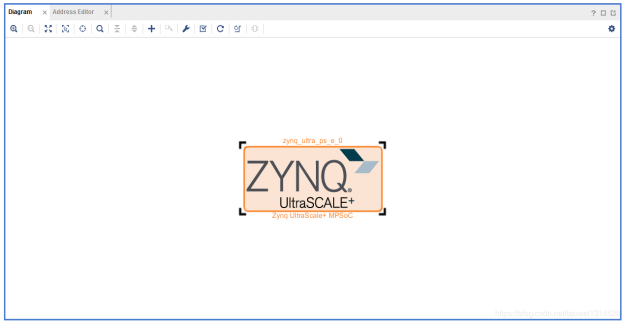

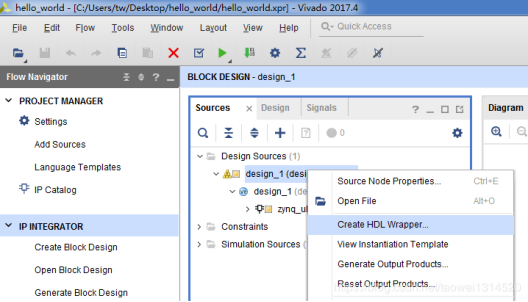

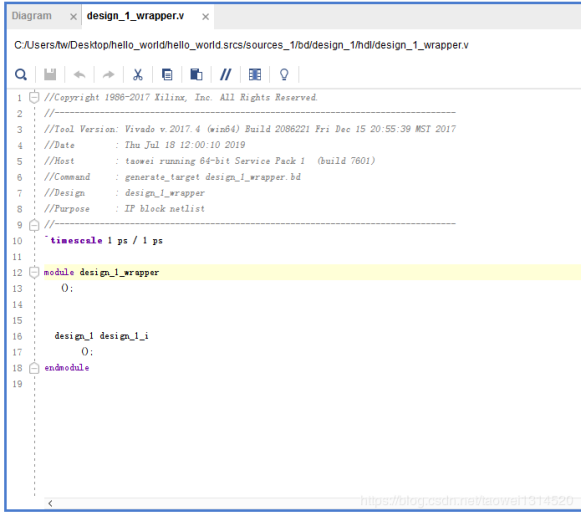

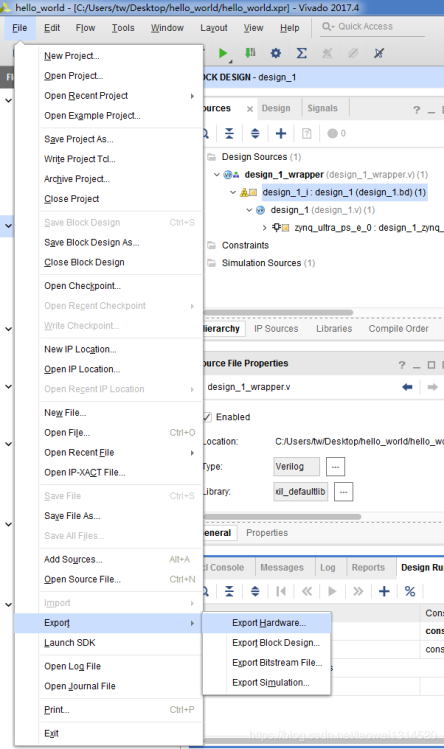

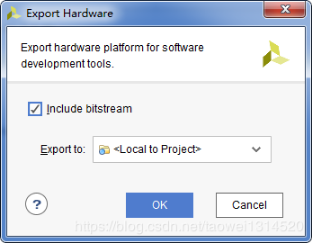

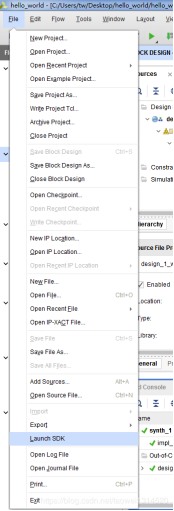

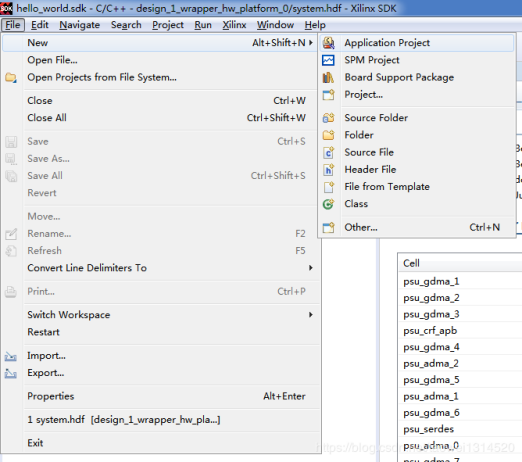

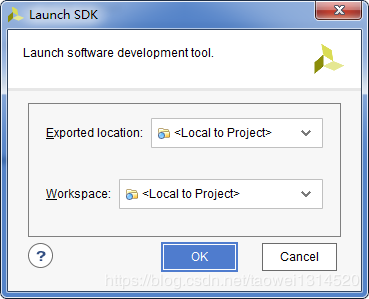

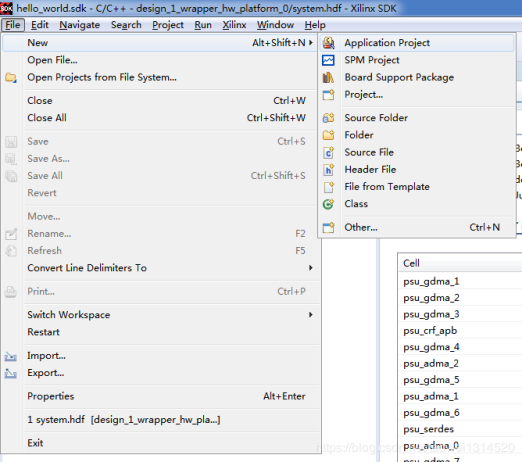

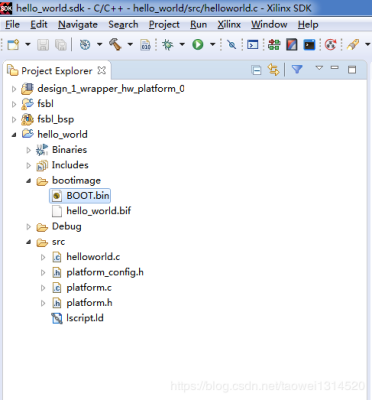

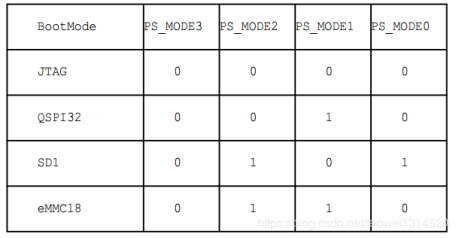

新建的Block设计区:  Step3 调用ZYNQ IP核并配置 点击Add IP  在导航栏输入ZYNQ,然后双击ZYNQ UltraScale+MPSoC  添加的ZYNQ核,如下图所示  双击ZYNQ IP核导入配置文件 点击Presets-->Apply Configuration 添加配置文件  导入 hello_world.tcl配置文件,点击OK  点击OK 配置完成后的ZYNQ 核如下图所示  Step4 综合 右击design_1 --> Generate Output Products  点击Generate Step 5 生成顶层文件 右击design_1-->Create HDL Wrapper  点击OK 生成的顶层文件,如下图所示  Step6 生成bit文件 点击快捷工具栏上的Generate Bitstream  下面点击OK bit生成成功,点击Cancel关闭对话框 Step7 导出硬件配置文件 点击File-->Export-->Export Hardware  勾选Include bitstream,点击OK  Step8 打开SDK 点击File-->Launch SDK  点击OK Step9 新建fsbl 点击File-->Application Project  添加工程名fsbl,点击Next  选择Zynq MP FSBL,点击Finis Step10 新建hello_world工程 点击File-->Application Project  填写工程名 hello_world, 点击Next,选择Hello_World模板,点击Finish  Step11 生成BOOT.bin文件 右击hello_world-->Create Boot Image  点击Create Image,生成的BOOT.bin文件,如下图所示,然后将这个生成的BOOT.bin文件拷贝到SD卡上  MPSOC开发板模式设置,这里我们设置为SD卡启动模式

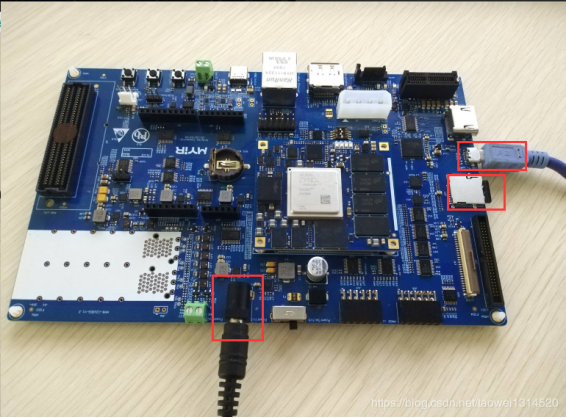

MPSOC开发板连接12V电源、连接uart串口、插入SD卡

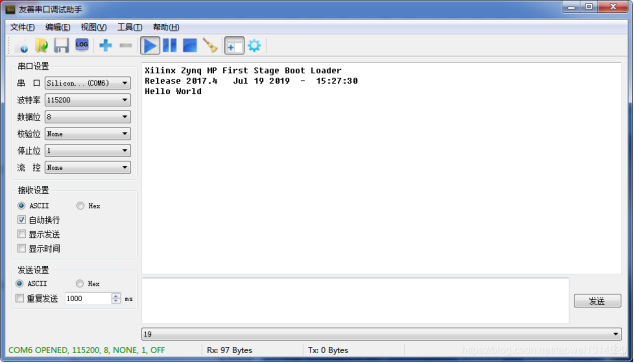

上电运行  串口打印输出 Hello World  关键词:MPSOC |

|

此帖由myyangyang于2019-07-23 16:34:22最后编辑

|

|

| 共1条 1/1 1 |

Xilinx

Xilinx