|

版主: 51FPGA |

Virtex-6 FPGA IO BANK 上电顺序要求

[您是本帖的第7718位阅读者]|

cc天地一沙鸥

最后登陆时间:2016-07-11 17:20:46 |

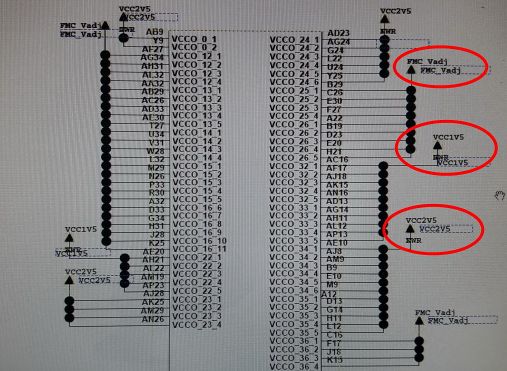

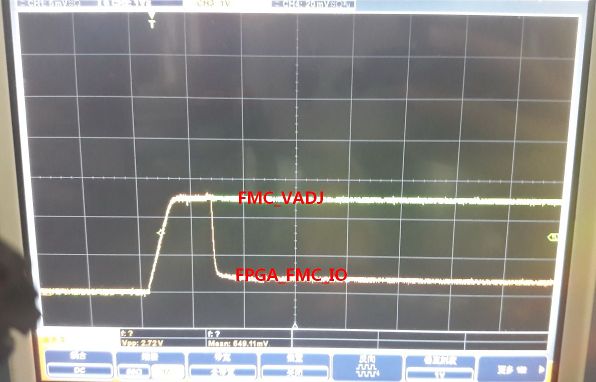

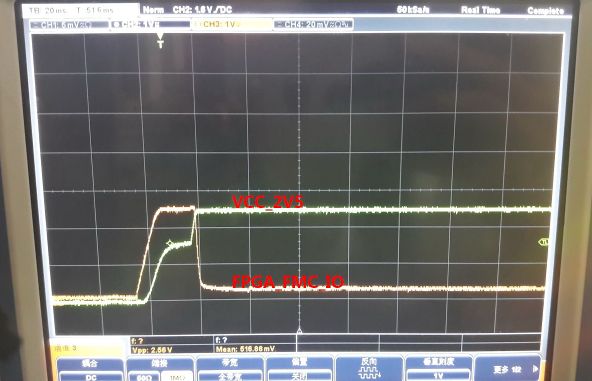

目前项目中遇到下述问题,查阅datasheet没有找到相关资料,希望得到大家的帮助。 项目中V6的IO BANK有三种供电,分别是可以通过FMC标准连接子卡进行ADC数据处理用的2.5V电源FMC_VADJ,2.5V电源VCC_2V5,1.5V电源VCC_1V5。 最初的上电顺序是FMC_VADJ上电,之后在电压监控芯片的作用下,同时使能VCC_2V5与VCC_1V5,发现在FMC_VADJ上电后,V6相关IO(FPGA_FMC_IO)同时有相同电压,但是VCC_2V5与VCC_1V5上电后,FPGA_FMC_IO立刻降落;而且先上电的FMC_VADJ会将未使能的VCC_2V5提前带起,却不会带起VCC_1V5。现象如下图所示:

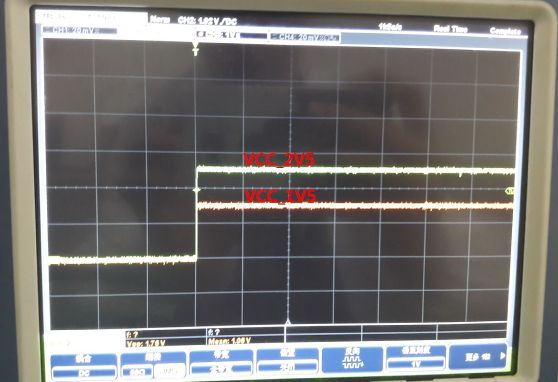

后来,更改上电顺序,将FMC_VADJ调整到VCC_2V5与VCC_1V5之后,FMC_VADJ不会对VCC_2V5造成影响,FPGA_FMC_IO随FMC_VADJ会维持在大约0.4V的电平上,现象如下图所示:

现象分析,V6的不同BANK对于上电顺序应该有具体的要求,datasheet中提到过IO BANK分组问题,但没有具体阐述,在不知道内部电路条件下分析受阻,希望遇到或了解相关问题的朋友可以一起讨论,谢谢。

关键词:V6 上电顺序 |

| 共1条 1/1 1 |

Xilinx

Xilinx