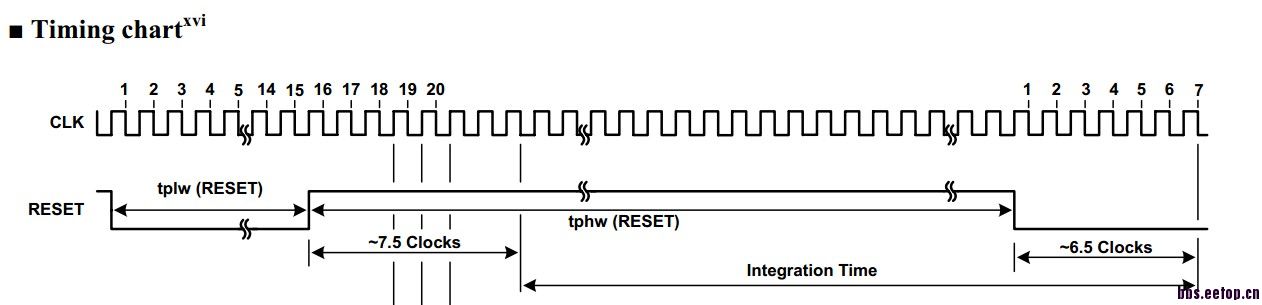

想使用FPGA产生以下时序来驱动一个线阵的探测器芯片

当然要实现CLK是很容易的 只要把系统时钟Mclk(50MHZ)分频就可以产生希望的40khz的CLK 关于RESET我的想法是使用状态机

但实现起来发现并不能产生相应的波形 希望大家看看程序的问题

module XB8804(Mclk, nRst,

FPGA_CLK, FPGA_RESET

);

input Mclk,nRst;

output FPGA_CLK,FPGA_RESET;

reg FPGA_CLK;

reg FPGA_RESET;

reg[9:0] FPGA_CLK_CNT;

reg [10:0] clk_cnt;

reg[3:0] state;

wire Scan_Flag; //扫描标志位

parameter IDLE=4'b1000,

RESET_L1=4'b0100,

RESET_L2=4'b0010,

RESET_H=4'b001;

assign Scan_Flag=1;//Scan_Flag应该是由外部的控制单元给过来 这里直接赋值了

always @(negedge nRst or posedge Mclk)

if(!nRst) begin

clk_cnt<=0;

FPGA_CLK<=0;

FPGA_RESET<=1;

FPGA_CLK_CNT <= 0;

state <= IDLE;

end

else begin

if(clk_cnt==11'd625)

begin

clk_cnt<=0;

FPGA_CLK<=~FPGA_CLK;

FPGA_CLK_CNT <= FPGA_CLK_CNT+1;

end

else

clk_cnt<=clk_cnt+11'd1;

case(state)

IDLE:

begin

FPGA_CLK<=1;

FPGA_RESET<=1;

if(Scan_Flag==1)

begin

state<=RESET_L1;

FPGA_CLK_CNT <= 0;

end

else state<=IDLE;

end

RESET_L1:

begin

FPGA_RESET<=0;

if(FPGA_CLK_CNT==15)

begin

state<=RESET_H;

end

else state<=RESET_L1;

end

RESET_H:

begin

begin

FPGA_RESET<=1;

if(FPGA_CLK_CNT==10'd529)

begin

state<=RESET_L2;

end

else state<=RESET_H;

end

RESET_L2:

begin

FPGA_RESET<=0;

if(FPGA_CLK_CNT==10'd7)

begin

if(Scan_Flag==1)

state<=RESET_L1;

else state<=IDLE;

end

else state<=RESET_L2;

end

default:state<=IDLE;

endcase

end

endmodule

|