|

版主: 51FPGA |

ASIC都去哪儿了

[您是本帖的第896位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

上周在看了我的朋友Dave Jones拆解一台旧的Fluke 91 ScopeMeter DSO(数字采样示波器)的视频时,我突然发现,这款有20年历史的测试设备标志着ASIC设计历时10年的衰落正开始显著加速。

Dave打开eBay ScopeMeter,发现其内部有数字和模拟两个主要的电路板。ScopeMeter的数字电路板包含两个ASIC和一个83C196掩码编程的16位微控制器(来自Intel的早期MCS-96系列)。SoC时代开始于1995年,Fluke于1994年构建这款DSO,刚好在处理器开始采用ASIC技术之前,因此我们能够看到有单独的板载微控制器。

ScopeMeter数字电路板上的数字ASIC似乎是闪存存储器/键盘控制器(标记为“Fluke MASIC”,由日立公司制造)和时基/触发器/事件计数器/显示处理器(标记为“Fluke D-ASIC”,由LSI公司制造)。第三块ASIC则由飞利浦公司制造,这是DSO模拟电路板上的模拟芯片,其集成有放大器、模拟开关和跟踪保持电路,可提供两个模拟信号通道。也就是说采用两个数字ASIC和一个模拟ASIC的相对较小型的仪器近20年前售价为一两千美元。

下面是Dave的EEVBlog视频截图,左侧为ScopeMeter的数字电路板。我分别在两个数字ASIC和Intel 83C196微控制器上画了红圈。

Fluke ScopeMeters作为一种测试设备,销量较高。不过让人很难相信今天设计的任何此类仪器会采用两个数字ASIC和一个微控制器。事实上今天根本就不会出现这样的设计。要是Fluke晚几年再设计这款ScopeMeter,很可能这两个数字ASIC和一个掩码编程的微控制器都会设计成一个SoC,或许极有可能是ARM微处理器内核。 多个数字ASIC和处理器芯片集成到单个器件是20世纪90年代中期以来ASIC设计数量大幅减少的一个重要原因。EDA发布的研究报告显示,ASIC设计数量从1997年开始进入顶峰时期,每年约11,000个,随后则面临以下三重挑战:

在上述三大趋势影响下,ASIC的设计数量从1997年的峰值到现在已经削减了约80%。

在某些市场领域,ASSP也出现了类似的趋势,在设计和NRE成本方面跟ASIC的问题大同小异。此外,ASSP厂商也要面临多种不同市场的要求,因为ASSP的目标市场跟其它所有市场一样也在越来越细分化。这一趋势会导致任何特定ASSP的销量下降,从而催生了涵盖多种不同要求组合的“超集 (superset)”ASSP的开发。不过一个用户如果选择了“超集”ASSP,那就是说只使用ASSP的一部分功能,而ASSP的成本却高于他们实际所需的。说到底,ASSP用户,也就是系统厂商,要为超集ASSP支付更多成本,而现在的ASSP越来越无法充分满足某种特定的设计要求了。

这时就要让可编程逻辑器件发挥作用。(您已经料到我要这么说了吧?)最新型28nm器件,如赛灵思7系列FPGA和Zynq All Programmable SoC,都能在众多设计中取代ASIC和ASSP。

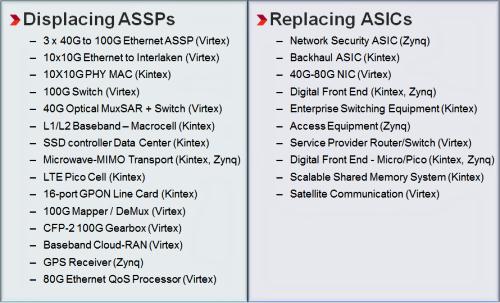

举例来说,安捷伦(Angilent)公司近期宣布在其新一代Fusion HPLC(高效液相色谱)仪表系列中采用赛灵思Zynq-7000平台,新系列产品将取代公司现有的1200系列HPLC。(敬请参见我在ARM网站上的嘉宾博客“安捷伦生命科学采用赛灵思技术确保软硬件仪表平台可充分满足未来要求 (“Agilent Life Sciences future-proofs HW/SW instrument platform with Xilinx)”。)Agilent 1200系列仪表模块采用了内嵌在FPGA中的PowerPC微处理器。 针对安捷伦的新一代HPLC仪表模块, Fusion设计团队将新设计集成到同一芯片上:也就是带有双处理器的赛灵思Zynq-7000系列的一款产品。设计团队对当前HPLC仪表系列固件和VHDL硬件设计的大部分均实现了再利用。起初,新设计只使用Zynq All Programmable Soc的一个片上ARM处理器,不过Fusion设计团队认为Zynq-7000 SoC上的第二个ARM处理器的更多处理资源也能发挥很大作用。因为种种原因,这种单芯片技术的软/硬件可重编程功能的结合为安捷伦设计团队带来了巨大竞争优势,ARM网站博客介绍了具体情况。 虽然安捷伦这个例子讲的是分析仪表应用领域,但同样的情况也适用于日常大多数市场。特别是在通信、网络和数据中心市场上这种情况尤为明显。随着通信速率的提升,上述市场不断需要最先进的芯片生产工艺,从而实现所需的性能。但是,设计成本快速提升,细分市场越来越小而且快速增加,这些压力同样存在,再加上快速变化的标准也是市场的基本现象,因此ASIC和ASSP解决方案在经济上越来越没有吸引力了。软硬件All Programmable解决方案则越来越具吸引力。 现在您或许要想,我是不是太有点自吹自擂了。如果说我还没有给您足够的论据证明,那说明我的工作做得不好。下面给出赛灵思All Programmable器件在通信、网络和数据中心应用领域已经取代200多款ASIC和ASSP的部分情况概览:

根据上述论据,我希望您也能同意我的观点,那就是越来越多应用领域正在用All Programmable器件取代ASIC和ASSP,这是大势所趋。我今后几个月还要在All Programmable 星球社区进一步深入地详细分析这一趋势,目的就是让您了解更多信息,并通过我介绍的方法解决您自己的一些设计问题。如需了解更多详情,现在您可以登录:www.xilinx.com/cn/smarternetworks。

|

| 共1条 1/1 1 |

Xilinx

Xilinx