|

xilinx论坛

- 我是MM

-

高级会员

最后登陆时间:2015-03-19 10:58:07

|

1#

发表于 2015-06-10 20:38:28

Picroblaze 介绍:

PicoBlaze微控制器是赛灵思推出的一个高性能低成本的8位处理器软核,它由Veriolog或VHDL语言实现,可以在FPGA/CPLD上实现,具有设计灵活方便,运行速度快,占用资源少的特点。虽然现在32位处理器大为盛行,但在一些低速的复杂控制方面使用PicoBlaze微控制器具有较大的成本优势,在这些应用中使用PicoBlaze微控制器将是一个比较好的方案。PicoBlaze微控制器的实现代码对用户是公开的,可使用户完全掌握设计中的所有细节,方便调试与使用,设计者甚至可以修改代码、增加和减少功能块来定制自己专用的处理器,体现了极大地灵活性,在低成本的场合使用还是相当不错的。

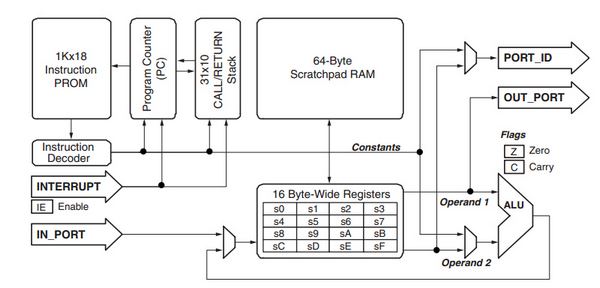

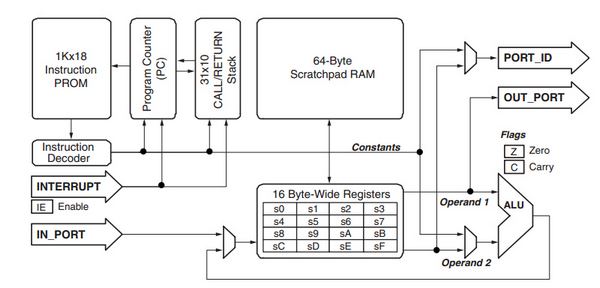

PicoBlaze结构概述

PicoBlaze微控制器由16 字节的通用寄存器、1K×18 BIT ROM、1个字节宽度ALU、64 字节的内

部RAM和程序计数器等组成,具体框图如下图一所示(摘自赛灵思文档ug129.pdf):

PicoBlaze微控制器提供57条不同的指令,256个直接或间接的可设定地址的端口,1个可屏蔽的中断,依赖于具体实现的FPGA型号,可获得44~100 MIPS的性能。更详细的描述请参考附件中UG129和KCPSM3_Manual,附件KCPSM3中也包含Pircoblaze3的代码及编译器,这些内容在XILINX的官网可以下载到。网上还可以找到基于Pircoblaze的IDE仿真环境,下载地址:http://www.mediatronix.com/pBlazeIDE.htm,这个软件也会包含在附件pBlaze_ide中。

关于PicoBlaze的详细使用会在后续的帖子中给出相关例程。

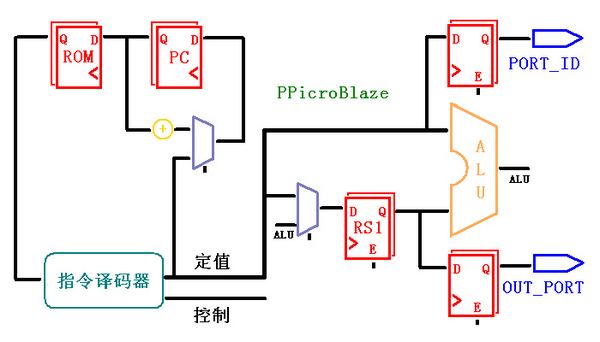

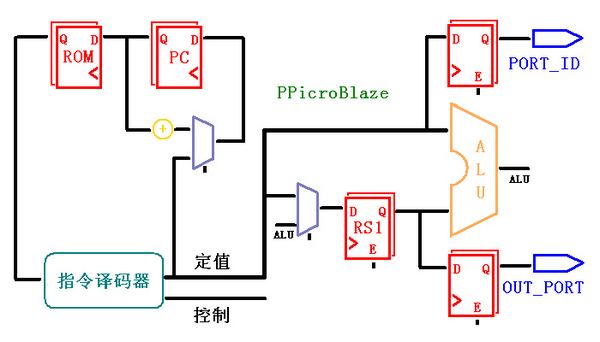

由于源码采用的基于LUT的描述方式,所以在阅读和理解上比较麻烦,为了更好的理解Picroblaze这个简单CPU,花了一天的时间使用Verilog的行为级描述重写了一个非常简单的PPicroblaze,开始支持的指令只有四条,寄存器只写了S1,指令空间为1K,后面有时间的话,希望能够完成整个Picroblaze。重写的目的仅仅是想深入的了解的架构。CPU结构图如下:

Ppicroblaze代码如下:

-

module ppblaze(clk,rst,port_id,out_port);

-

/***** *****/

-

input clk,rst;

-

output[7:0] port_id;

-

output[7:0] out_port;

-

//--- ---

-

wire [9:0] address;

-

wire [17:0] instruction;

-

wire [5:0] cmd;//just for simulate

-

-

assign cmd = instruction[17:12];

-

/*** ***/

-

reg clk_div2;

-

-

always @(posedge clk or posedge rst) begin

-

if(rst) clk_div2 <= 1'd0;

-

else clk_div2 <= ~clk_div2;

-

end

-

/*** ****/

-

reg pc_sel,rs1_sel,rs1_load,id_load,out_load;

-

-

always @(rst or instruction) begin

-

if(rst) {pc_sel,rs1_sel,rs1_load,id_load,out_load} <= 5'b00000;

-

else

-

case (instruction[17:12])

-

6'b000000:{pc_sel,rs1_sel,rs1_load,id_load,out_load} <= 5'b00100;//load

-

6'b011000:{pc_sel,rs1_sel,rs1_load,id_load,out_load} <= 5'b01100;//add

-

6'b101100:{pc_sel,rs1_sel,rs1_load,id_load,out_load} <= 5'b00011;//out

-

6'b110100:{pc_sel,rs1_sel,rs1_load,id_load,out_load} <= 5'b10000;//jump

-

default:{pc_sel,rs1_sel,rs1_load,id_load,out_load} <= 5'b00000;

-

endcase

-

end

-

-

/*** pc control ***/

-

reg [9:0] pc_r;

-

-

always @(posedge clk_div2 or posedge rst) begin

-

if(rst) pc_r <= 10'd0;

-

else if(pc_sel) pc_r <= instruction[9:0];

-

else pc_r <= pc_r + 1'd1;

-

end

-

-

assign address = pc_r;

-

/*** rs1 regitor ***/

-

reg[7:0] rs1;

-

wire[7:0] rs1_data;

-

wire[7:0] add_reault;

-

-

assign rs1_data = rs1_sel ? add_reault:instruction[7:0];

-

-

always @(posedge clk_div2 or posedge rst) begin

-

if(rst) rs1 <= 8'd0;

-

else if(rs1_load) rs1 <= rs1_data;

-

end

-

/*** add ***/

-

assign add_reault = instruction[7:0] + rs1;

-

/*** out instrution ***/

-

reg[7:0] port_id;

-

reg[7:0] out_port;

-

-

always @(posedge clk_div2 or posedge rst) begin

-

if(rst) {port_id,out_port} <= {8'd0,8'd0};

-

else begin

-

if(id_load) port_id <= instruction[7:0];

-

if(out_load) out_port <= rs1;

-

end

-

end

-

/*** ***/

-

led program

-

(

-

.address(address),

-

.instruction(instruction),

-

.clk(clk));

-

-

endmodule

Led program是使用汇编程序生成的RAM代码,verilog或VHDL格式都有,可以使用附件的KCPSM3汇编器生成,在DOS窗口下输入汇编器的当前路径,调用改汇编器即可。

Led program源代码很简单,仅包含四条语句,完成一个简单的流水灯程序(没有延时,实际用估计一闪而过了)。

-

CONSTANT led, 01

-

LOAD s1,01

-

start:

-

ADD s1,01

-

OUTPUT s1,led

-

JUMP start

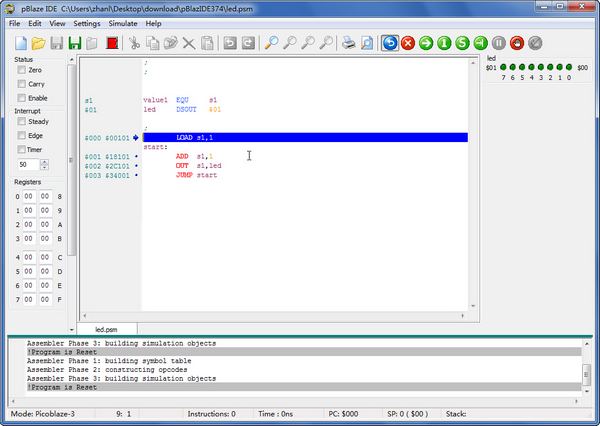

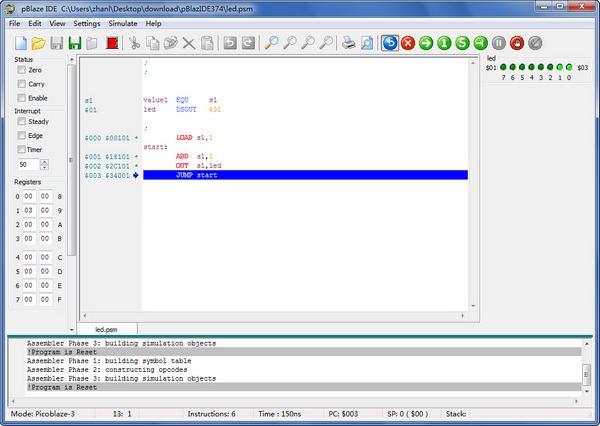

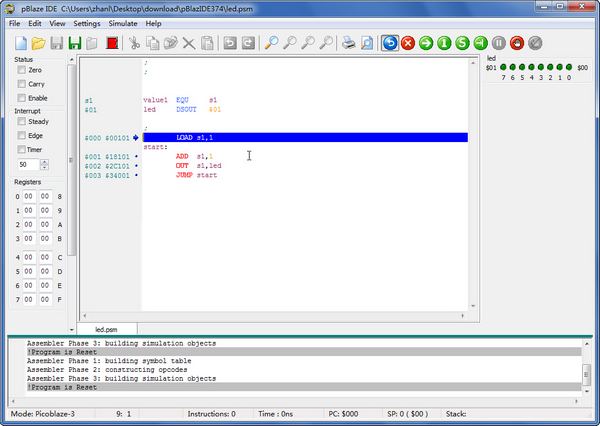

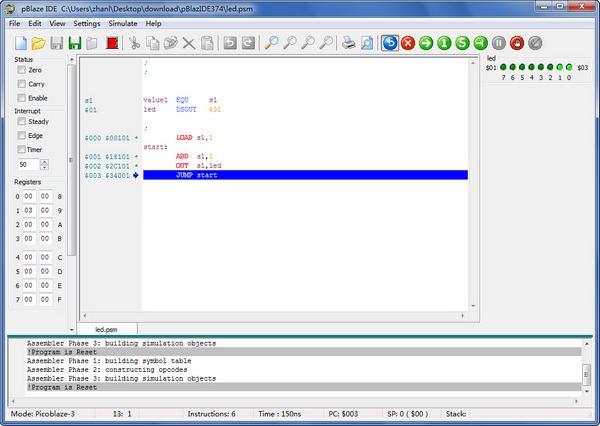

我们先使用pBlazIDE编辑、仿真环境来仿真一下。pBlazIDE界面如下,还是比较美观的。pBlazIDE仿真的程序和编译的程序格式不大一样,这点需要注意,需要仿真程序是,从file菜单下选着导入即可。可以看到随着程序的运行,右边的led在逐渐变化

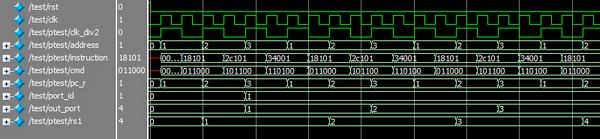

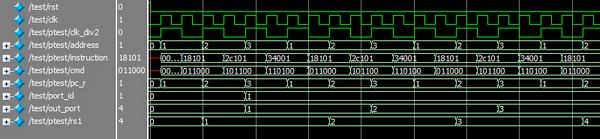

接着我们做硬件仿真,在附件中提供了完整的仿真代码,包括测试激励和BlackRam库文件,打开modelsim,选着当前的路径后,在Transcipt中输入do run.do 即可看到仿真波形

attachment.zip

|

Xilinx

Xilinx