|

版主: 51FPGA |

FPGA专家教您如何在FPGA设计中使用HLS

[您是本帖的第1276位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

SemiWiki 有了一位新的博主,被称为“The FPGA Expert(FPGA专家)”。通过LinkedIn简单搜索,我得知这位FPGA专家是Luke Miller,他最近发表了一篇博文,介绍如何使用高层次综合(HLS)开发从C到其他HLL版本的各种加速硬件。 虽然不像“手把手的菜谱”那样具体详尽,但依然非常有趣。

Miller曾经在IBM公司担任过ASIC设计师,在Lockheed担任过硬件师(工程师/架构师),目前是一位拥有军事和航空设计经验的PE。Miller的网站名为FPGA Expert,上面有一段特别的讲述其个人经历的视频,其中描述了多项军事、航空和医疗项目(飞机、雷达和医疗成像),所以,我猜他应该拥有非常丰富的FPGA设计经验。他的网站证实了这个猜想。 Miller似乎也非常了解HLS。他写道:

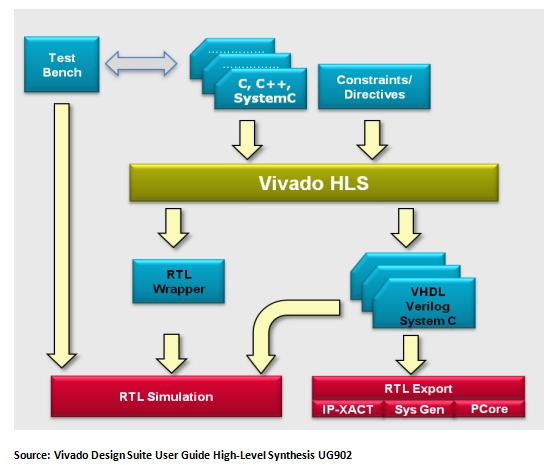

“设计时间的加速并非从C到VHDL的转换, 真正起到关键因素的是仿真域 —您再也无需通过RTL逐件验证每项设计。” Luke Miller并非一直都是HLS(高层次综合)的倡导者。在使用早期的工具版本的时候,他似乎有些糟糕的经历。。他写道:“……我的心筑起心墙,我需要帮助。”幸运的是,他似乎已经通过了一个12步HLS培训活动, 现在可以通过Xilinx Vivado HLS有效地开展工作了。

点击此处,阅读Miller有关HLS的建议:“高层次综合 —它真的行! ( High Level Synthesis – It’s for Real) ”http://www.semiwiki.com/forum/content/2222-high-level-synthesis-%96-%92s-real.html

下面是Miller的全文供参考:

High Level Synthesis – It’s for Real by Published on 04-11-2013 06:30 PM

It was spring 2010 and I was asked to attend an HLS (High Level Synthesis) meeting. To be honest I cringed, after my bad relationship with Accel DSP and broken promises my heart was all walled up and needed counseling. But my management had a way of making me an offer I could not refuse, like keeping my job. So reluctantly I went. Does your employer do lunch and learns instead of real training? You know what that equals right? A 1/8 pay cut, but let’s play nice.

I leverage HLS tools in this fashion. I view it as Xilinx Corgen on steroids which are driven by a C file. The speed up in design time is not in the translation from C to VHDL but really is in the simulation domain. You are no longer verifying designs piece by piece using RTL. For example, I design a Beamfomer in C. I compile it and then run ‘a.exe’ and verify that the answer matches the expects. That took about a second. For many PRIs of data that could of taken hours in ModelSim. Catching on? I then bring up the HLS tool and pull in the C file and the tool reports the latency, area, clock frequency etc. From that information I can determine which FPGA to use. I then start using directives to optimize the area / latency by using unrolls and pipeline directives. About an hour later my beamformer is done. I then simulate the RTL at my top level but I already know the math works and the tool took care of the boundary conditions. The goal of this article is by no means a recipe on HLS usage but hopefully entices you to check it out, you won’t be sorry |

| 共1条 1/1 1 |

Xilinx

Xilinx