|

版主: 51FPGA |

Verilog HDL语言always块未声明positive或negative导致的时钟不对准

[您是本帖的第919位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

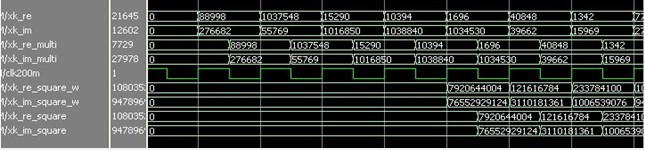

题目:Verilog HDL语言always块未声明positive或negative导致的时钟不对准 程序一直有一个问题,明明对好的时钟,复查了很多遍,但仿真结果就是不对,错开了两个时钟,不知何故。 由于先前没仔细查ModelSim仿真波形,只能又花了一晚上把数据跑了一遍,这次清楚了,但看到了两个奇怪的现象,如下图所示:

其中xk_re_multi和xk_im_multi分别是xk_re和xk_im的延时,xk_re_square和xk_im_square 分别是xk_im_square_w和xk_re_square_w的延时。 但从图中发现,xk_re_multi和xk_im_multi以及xk_re_square和xk_im_square都是在时钟clk200m的下降沿变化的,这是怎么回事?程序中明明都是用的上升沿呀! 看了一下程序,原来是这样: always @ (clk200m) if(!rst200m || !accurate_freq)begin xk_re_multi <= 20'd0; xk_im_multi <= 20'd0; xk_re_square <= 40'd0; xk_im_square <= 40'd0; end else begin xk_re_multi <= xk_re; xk_im_multi <= xk_im; xk_re_square <= xk_re_square_w; xk_im_square <= xk_im_square_w; end 可以看出,在括号里只写了clk200m,未声明是时钟上升沿还是下降沿。 我感觉应该是导致时序逻辑变成了组成逻辑,即当clk200m变化时执行下面的语句。(不知对不对,不深究了,我的问题解决了就好啦) |

| 共1条 1/1 1 |

Xilinx

Xilinx