|

版主: 51FPGA |

从零开始,搭建zynq-7000的PS硬件平台--基础PS系统

[您是本帖的第1206位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

主机环境:ubuntu10.04lts X64_64bit,root 开发工具:planAhead 参考资料:Zynq-700EPP CTT(UG873)/ ZedBoard(ZynqTM Evaluation and Development Hardware User’sGuide)

Zynq与一般的ARM处理器不太一样,它的PS系统(处理器部分)也是可以定制的,比如各种存储器的接口,通用总线接口等等,即使我们不用zynq上的PL系统(FPGA部分),也可以定制一个自己的ARM 芯片, xilinx管这个叫“All programmable”,很酷吧。 所以呢,即使是纯软件开发,我们也需要首先配置一个PS,下面将搭建一个空白的基本系统(blank base system),即没有配置任何功能的PS。 1,启动PlanAhead 工具 在ubuntu系统下,打开终端,输入以下命令: 1)source/disk2data/Xilinx_ISE141/14.1/ISE_DS/settings64.sh 2)planAhead 然后,PlanAhead开发环境启动

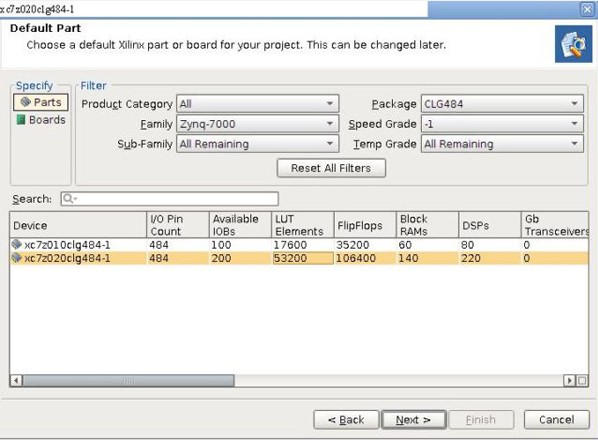

图1,启动PlanAhea环境 2,建立新的工程 1)点击 “Create New Project”启动新建工程的向导 2)出现Project Name画面,输入以下内容: Project name:工程名字,这个自己指定 Project location:指定项目的存储文件夹 CreateProject Subdirectory :是否建立子文件夹,打上勾 3) Project Type画面:选择RTL Project 4)Add Sources:不填,直接next 5)add Exiting IP:不填,直接next 6)add constrains:不填,直接next 7)Default Part:对于Zedboard来说,暂时没有现成的”Boards”库,按照下面的图中的参数选择xc7z020clg484-1,需要注意的是,实际上ZedBoard用的芯片型号为xc7z020csg484-1,这个芯片在ISE14.1Parts库也是没有的,因为clg和csg是芯片的封装形式,我们暂时推测这2个芯片的其他定义可能相同,因此用clg代替csg做成的硬件配置文件也是可以通用的。当然即使xilinx正式发布了csg的zynq芯片后,如果确实有不同的定义,也没太大关系,那个时候一定新的库了,直接导入即可。

图2,选择zynq器件 8)New Project Summery:检查一下设置,点击Finish完成向导。

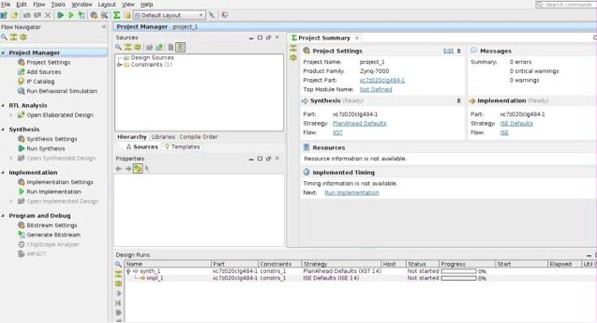

图3,完成向导后,PlanAhead界面 完成向导后,出现PlanAhead界面,注意下面的Design Runs中的Strategy要是Defaults (XST 14) 和ISE Defaults (ISE 14) 2个值,否则就是什么地方有错误,需要检查排除才能继续下面的操作,这个很重要。

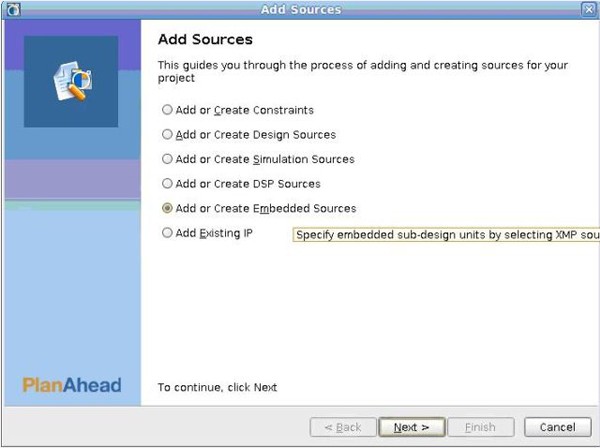

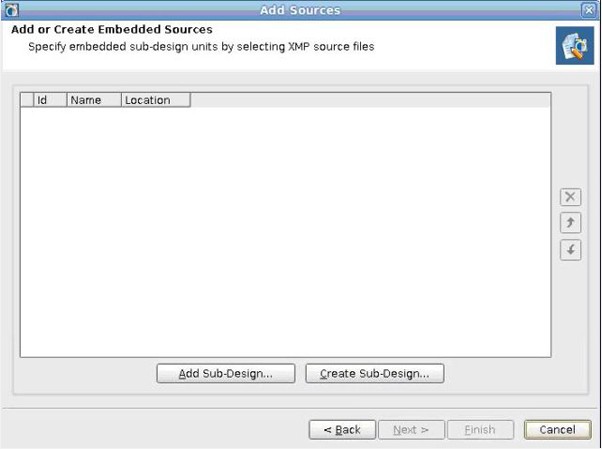

9)添加空白的PS系统 10)选择“Add or Create Embeded Sources”,点击next

图4,Add Soureces界面 11)在 Add or Create Embedded Source,点击“Create Sub-Design”,输入模块名字,比如system。

图5,CreateSub-Design 最后点击yes,完成设计,系统将启动XPS,然后会有提示例化Processing System7,点击Yes。

图6,例化ProcessingSystem7 12)查看Blank Base Bystem

图7,XPS下PS系统查看 在Zynq选项卡下,是一个完整的zynq系统,没有任何配置。绿色表示这个部分是可以“Programmale“的,即我们能够对其配置,只要点击任何一个绿色区域都会出现配置向导,帮助我们完成定制。 文章转载自: http://blog.csdn.net/morewd

|

| 共1条 1/1 1 |

Xilinx

Xilinx