|

版主: 51FPGA |

从零开始,搭建zynq-7000的PS硬件平台--DDR3接口集成与配置

[您是本帖的第1917位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

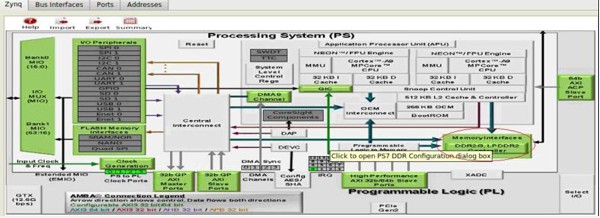

操作环境:ubuntu10.04lts X64_64bit,PlanAhead/XPS14.1 参考资料:ZedBoard_HW_UG_v1_1, ZedBoard原理图, Zynq-700 EPP CTT MT41K128M16HA-15E datasheet 建立完PSbase system后,可以配置了,下面开始DDR3的设置,在XPS下操作。 在Zynq的tab下点击“memeryinterface”(图1中红圈标识的模块),出现PS7 DDR Configuration 窗口,如图2所示。

图1,Zynq选项卡

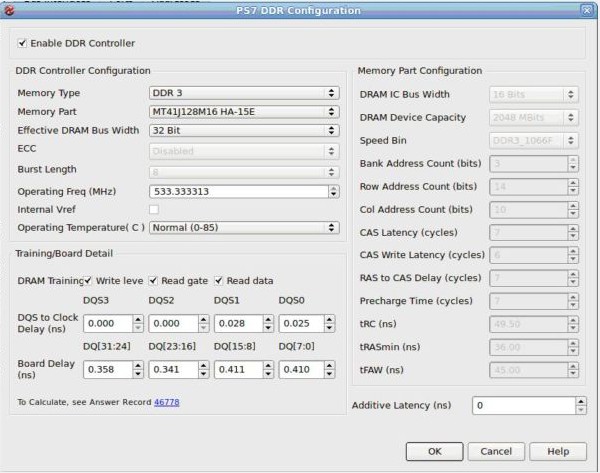

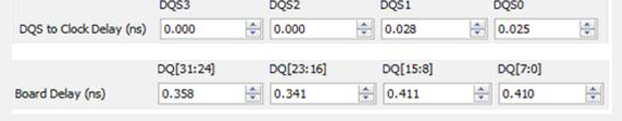

图2,PS7 DDR Configuration 窗口 因为ZEDboard板卡上使用DDR3作为外部存储器,所以“Enable DDR Controller”要选上。然后就是“DDR ControllerConfiguration”中的参数选择了: Memory Type:ZEDboard使用的是DDR3 Memory Part:使用的DDR3芯片型号为MT41J128M16HA-15E,这来源于原理图。在ZedBoard 的硬件用户手册上说使用了MT41K128M16HA-15E型号的DDR3颗粒,与原理图有所不同,其实Micron的这2种颗粒都是DDR3的,不过MT41J仅是1.5V的,而MT41K是可以使用1.35V电压的,当然也兼容1.5V。 Effective DRAM Bus With:ZedBoard使用了2片MT41J128M16HA-15E,单片总线宽度为16bit,故此处选择32bit。 Operating Freq(MHZ) :接口时钟,根据ZedBoard的硬件用户手册,为533MHz,实际填写的是533.333313MHz,这是由于PLL分频不能正好分出整数值。该DDR3型号后面的-15E说明该芯片最大标准数率为1333Mbps,因此最大的接口频率就是667MHz。 Operating Temperature:DDR3器件的工作温度,默认就是0-85摄氏度,不用改了 在Traning/Board Detail栏中,将Write level 、Read gate、Read data 3个选项打钩,根据硬件用户手册的说明,这可以让DDR3性能处于最佳状态。 在DQS to Clock Delay(ns)和Board Delay(ns)中,要填上以下数值:

这是为了补偿DDR3器件本身以及PCB布线的偏差而设的,具体的计算原理可以参考xilinx的AR46778,在官方上搜索即可找到。 文章转载自: http://blog.csdn.net/morewd

|

| 共1条 1/1 1 |

Xilinx

Xilinx