1#

发表于 2015-03-31 22:07:50

摘要:本文介绍与XILINX的EPP平台成员, ZYNQ芯片相关的缩写术语和含义. 与简单翻译术语不同,本文对每个缩写在本行业其他公司的展开含义也略作介绍, 避免混淆. 对术语的技术功能也作简单介绍.

8月份学校放暑假, 大学计划这边紧急的事不多,因此通常是俺的充电和学习时间.

本月的学习任务嘛, 当然是ZYNQ. 资料不多,一个是今年3月份出来的UG804,是一个简介性质的东东, 24页, 另一个是UG585,技术手册,目前有1804页. 目前都还是保密的, 合作伙伴需要签NDA才能看到.

去年ZYNQ刚出来的时候,文档还没有,俺只有对着仅有的一个框图,对其中的缩写瞎猜了一番. 当时还写了博客. 信马由缰-XILINX的ARM芯片初探(之一). 看到UG804,终于有机会验证俺当时猜的缩写展开到底对不对.

看了之后才发现, 框图中那点看不懂的缩写, 比起UG804中引入的各种缩写, 简直是小巫见大巫. 为了给你一个概念, 假设你3年后碰到一个用过ZYNQ的工程师, 和你说了下面一句话, 你能听懂多少:

经理啊, 我的PS启动了,可是PL还没加载, 这时,APU复位检查了没问题, MIO连得好好的,EMIO看上去也工作正常,你说我该查GIC呢, 还是AFI呢 ?

坑爹啊! 比火星文还火星文的话听了伤不起啊~~~. 下面,开始逐个解释新出现的,或者冷僻的缩写,继续看文档时看见了,才能反映上来是啥意思.

开始,还是用最基础的marketing 图。 真正的详细图嘛,要等UG804,UG585正式发布了才能放上来。

最高一个层级的缩写:

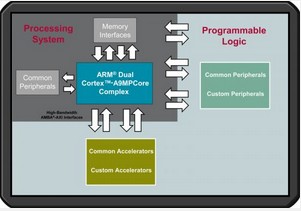

PS: 处理系统 (Processing System) , 就是与FPGA无关的ARM的SOC的部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。之所以叫PL,而不是叫FPGA,我想,原因主要是考虑到让搞软件的兔子们不要看了以后望而生畏。逻辑嘛,搞软件的也要讲逻辑是不?可编程,软件就是编程是不?

ZYNQ,往大里说,就是两大功能块,PS 部分和 PL部分, 说白了,就是ARM的SOC部分,和FPGA部分。

下一个层级, APU部分:

APU: 应用处理器单元(Application

Processor Unit). 位于PS里面的中心位置。这个名字起的,就有点学问了。

APU这三个字,AMD公司曾经用过,特指全称是“Accelerated

ProcessingUnits”,加速处理器,它是融聚了CPU与GPU功能的产品,电脑上两个最重要的处理器融合,相互补足,发挥最大性能。XILINX的APU与AMD的APU在缩写上就是截然不同的两个词, 不能混淆了。

APU 这个词,在Xilinx内部的术语中,也是撞车了的。 在XILINX 的 PowerPC体系中, 有一个辅助处理单元“Auxiliary Processing Unit”的概念,指的是在PowerPC硬核外挂的浮点协处理器之类的单元。

在这个位置上的处理器, 还有各种其他的叫法, 有MCU (微控制器处理单元Microcontroller Unit), MPU (微处理器单元Microprocessor

Unit),等等。 MCU这个叫法,暗示了处理器功能不强,只能搞搞输入输出控制啊,写个小状态机啊, 一般都是8位机。 MPU呢,就更先进了一些,成prcessor了,这意味着处理器通常是32位的, 能干点计算的事。 但是, 有一个micro词根在里面,说明干的是小活, 通常没有正式的和全尺寸的操作系统, 通常没有内存管理单元MMU。 ARM的Cortex-M系列是干这类活的。

APU, 带了Application这个词, 意味着在上面可以跑应用程序, 暗示着这个系统是需要全尺寸的操作系统的,和现在炙手可热的应用商店app store 遥相呼应。

APU里面具体包含的内容嘛,就是双ARM-CortexA9核,加上高速缓冲,DMA,定时器,中断控制,浮点和NEON协处理,硬件加速器一致性控制器ACP神马的。 也就是,处理器核心部分。

套用时下越来越流行的词汇,“嵌入式计算”, "embedded computing", 可以这么说,用MCU,MPU搭出来的东东,通常叫嵌入式系统。 而APU搭出来的东东,

就够格叫嵌入式计算系统了。

TTC, 这个词,当年猜了半天也拿不准,看了文档,发现,是Triple Time Counter的意思。 就是这个计数器里面有3个独立通道,可以独立计数。 挂在APB上,为系统或外设提供定时或计数服务的。

WDT, 看门狗定时器,有两个, 分别监视ARM-Cortex A9用的。 如果软件跑飞,无法清定时器,一段时间后,看门狗就复位。

SWDT,系统级看门狗定时器, 这个看门狗的时钟和复位信号,都可以来自于芯片外部, 这样,即使系统有严重故障,比如时钟频率本身都有问题了,仍然可以通过与系统无关的外部信号计数,计数满就复位。

SCU, Snoop

Control Unit, 用来保持双核之间的数据Cache的一致性。 也就是是说,第一个A9

处理器写存储时,只是写在了缓存里,没有进主存, 如果第二个A9读操作,涉及到第一个写脏了的数据段,SCU要保证第二个A9的缓存里是最新的数据。 如果第二个A9写同样数据段的数据,需要在第一个中体现出写的内容。 SCU的存在,才使得两个核成互相联系的“双核”,才能成为MPsoc。 在原先XILINX的双PowerPC的芯片中, 是木有这个东东的。不少学校的老师拿XILINX的双powerpc练手和教学,从头搭一个Snoop协议在裸的双PowerPC中,倒也不错。

|