|

版主: 51FPGA |

verilog小数如何表示

[您是本帖的第1207位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

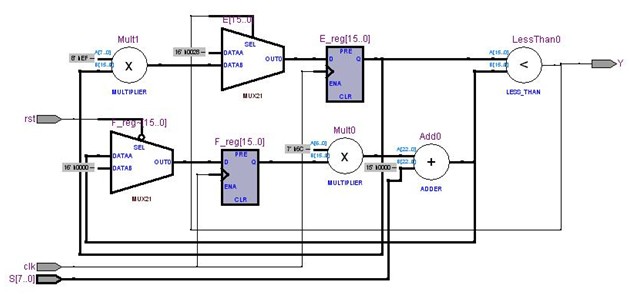

现在我要实现以下的算法,遇到了问题,首先是小数乘法的问题。想要实现的功能是通过迭代,Y周期性输出01010101.。。。。。 算法如下: F(t) = KF*F(t-1) + S; E(t) = KE*E(t-1) + VT*Y; if F(t)>E(t-1), Y =1;else Y=0;

其中KF、KE都是小数,那么怎样表示呢?verilog不支持小数啊?用定标表示不是很理解啊,小数定标了,那其他原来的整数呢?? verilog代码如下: module pcnn(clk,rst,S,Y); input clk,rst; input[7:0] S; output Y;

parameter KF = 108,KE = 239,VT = 5120;//Q8

//reg Y_reg; reg[15:0] F_reg; reg[15:0] E_reg;

wire Y; wire[15:0] F; wire[15:0] E;

assign F = KF*F_reg + S; //zuhe assign E = Y?KE*E_reg:VT; //assign E = KE*E_reg + (Y?VT:0); assign Y = (F>E_reg)? 1 : 0;//E_reg:number of the last time,not E.

always@(posedge clk) //shixu begin if(!rst) begin //Y_reg <= 0; F_reg <= 0; E_reg <= VT; end else //Y_reg <= Y; F_reg <= F; E_reg <= E; end endmodule<ignore_js_op>

|

| 共1条 1/1 1 |

Xilinx

Xilinx