|

版主: 51FPGA |

产生毛刺怎么办

[您是本帖的第903位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

之前做的网络可以时序仿真,但出现有规律的毛刺。输出加寄存器虽然去除了毛刺,但输出延迟了一个时钟,我共用了一个时钟信号。是不是要加一个和原来电路不同的时钟呢?或者代码中有问题?是不是代码的问题。

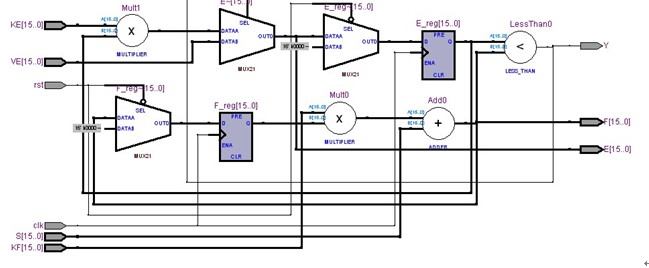

代码如下: module pcnn(clk,rst,S,Y,KF,KE,VE,F,E); input clk,rst; input[15:0] S; input[15:0] KF; input[15:0] KE; input[15:0] VE; output[15:0] F; output[15:0] E;

output Y;

reg[15:0] F; reg[15:0] E; reg[15:0] F_reg; reg[15:0] E_reg;

reg[31:0] MUL_F; reg[31:0] MUL_E;

///////////////zuhe

assign Y = (F>E_reg)? 1'b1 : 1'b0;//E_reg:number of the last time,not E.

always@(KF,F_reg,S) begin MUL_F = KF * F_reg; F = MUL_F[23:8] + S; end

always@(Y,VE,KE,E_reg) begin MUL_E = KE * E_reg; if(Y) //E=VE + MUL_E[23:8]; E=VE; else E=MUL_E[23:8]; end

always@(posedge clk) //shixu begin if(!rst) begin F_reg <= 0; E_reg <= 0; end else begin F_reg <= F; E_reg <= E; end end endmodule

RTL视图<ignore_js_op>

|

| 共1条 1/1 1 |

Xilinx

Xilinx