|

版主: 51FPGA |

[Virtex-6] 基于FPGA的IP核水印保护方法

[您是本帖的第1060位阅读者]|

xilinx论坛

最后登陆时间:2015-03-19 10:58:07 |

在数字电路设计领域中,FPGA可作为一种原型工具.用以解决在ASIC设计中,因重复设计而引起的一次性开支(Non Recuuring

Engineering,NRE)过高.以及上市时间(Time To Market,TIM)过长等问题。

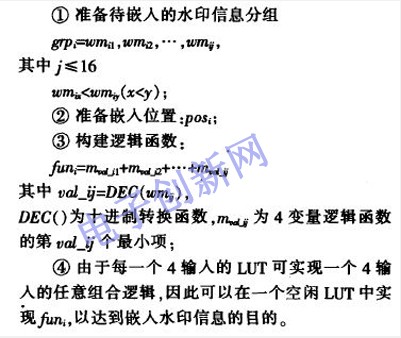

3.4 嵌入分组信息

|

| 共1条 1/1 1 |

Xilinx

Xilinx