1#

发表于 2015-03-28 23:48:27

Xilinx的FPGA加载时是需要时间的。在最初设计的时候,我们确实从来没研究过这个问题。因为每次上电后,加载的都很顺利,系统也能很快识别PCIE设备(顺便提一下,我们做的是带PCIE的网络设备),但在最近一次偶然事件中,发现了此问题的重要性。

当PROM的芯片驱动时钟频率较低时,其烧写FPGA的速度确实很慢。

在FPGA加载逻辑文件时,需考虑很多问题,如上电顺序,板卡的可靠性,和其他设备的互操作性。如果板卡上有PCIE控制器,需保证在系统识别PCIE之前,对FPGA的逻辑加载成功。不幸的是,很多设备一开始并没有考虑这个问题。

V6系列(本人用的,其他的类似)的FPGA在上电后配置加载的过程如下:

1 等待上电复位信号(power

on reset),这里的上电指FPGA的各类电源,如VCCINT,VCCAUX,VCCO等;

2 等待初始化(INIT)完成信号,只有初始化完成后,才能接受从外部(PROM或JTAG或其他方式)发送来的bit流逻辑文件;

一般地,上述步骤1和步骤2总的时间不超过50ms

3 等待bit流完成信号DONE,此等待的时间为bit流进入FPGA完成烧录的时间,取决于以下几个要素:

-

bit流文件的大小

-

烧写时钟的频率

-

Flash芯片的传输类型(SPI、BPI、PFP)

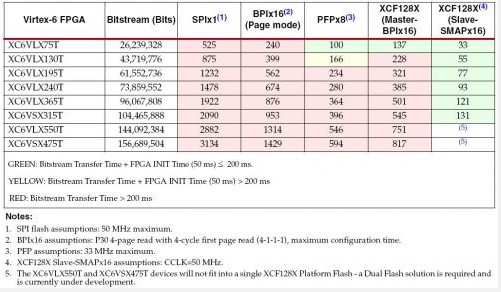

下图为V6系列在ATX主板上的bit流加载时间

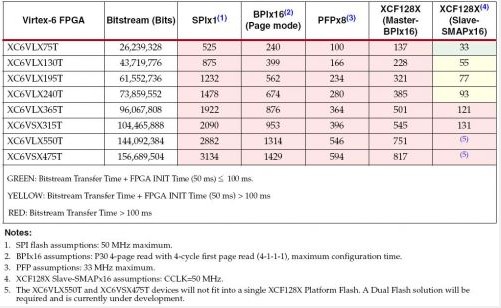

下图为V6系列在非ATX主板上的bit流加载时间

bit流的加载时间基本上是可以确定的。其和主板的要求是什么关系呢?

理想情况下可参考下面的公式:

FPGA Configuration Time ≤ T(PWRVLD) + T(PVPERL)

其中:

T(PWRVLD) ---- 指主板从上电开始到上电OK经过的时间,在ATX主板上,一般在100ms-500ms

T(PVPERL) ---- 指主板从上电OK到首次复位信号无效(高电平)的时间,最小值有100ms

所以上述公式可简化为:FPGA

Configuration Time ≤ T(PWRVLD) + 100ms

考虑到实际情况,主板会有两次复位,而两次复位中间的时间是不影响FPGA所在板卡上的加载时间的,所以实际情况下的修正公式为:

FPGA Configuration Time ≤ T(PWRVLD)+ T(PERSTPERIOD) + 100 ms

其中:

T(PERSTPERIOD) ----- 指第1次复位无效(高电平)的时间+第2次复位前的复位时间(低电平)。

此时间可能和主板的设计有关,从网上查找的资料看有的描述是1ms,有的描述是至少100ms,甚至大于300ms。

具体的若想探讨主板的上电顺序及时间,可从网上找相关资料查询。

至少本篇文章可以对V6系列的bit流加载设计起到指导作用。

|

Xilinx

Xilinx