|

版主: 51FPGA |

有人用过xilinx 的FIR的IP核么,为什么我的输入信号的采样频率是25K,但是输出信号的采样频率却不是25K呢?

[您是本帖的第1009位阅读者]|

simonmao8385

最后登陆时间:2014-12-08 13:00:36 |

【知青】哈尔滨Yamateh 有人用过xilinx 的FIR的IP核么,为什么我的输入信号的采样频率是25K,但是输出信号的采样频率却不是25K呢?????

【支书】哈尔滨-褴褛不

采样频率不应该是固定的吗?

【知青】哈尔滨Yamateh

对啊 所以说有问题嘛

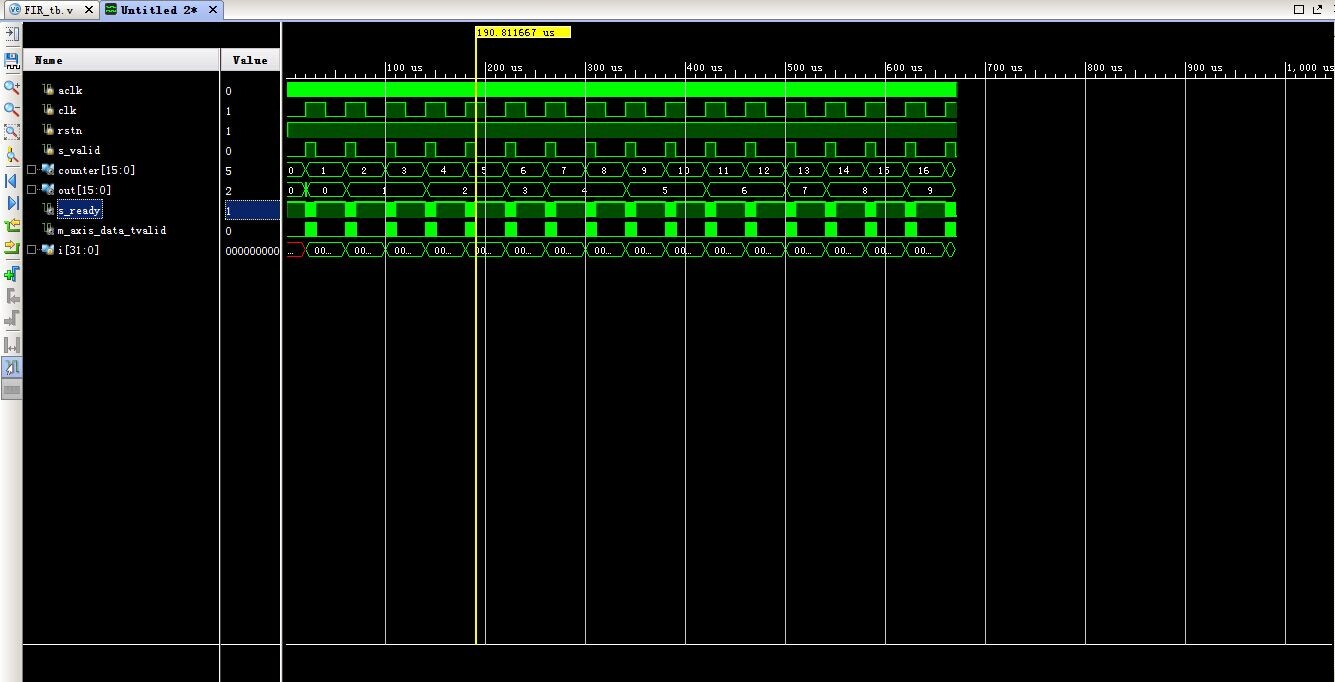

仿真的结果就是这样的,counter就是输入的数据,out是输出的数据

【知青】深圳-chenyh

你设置了变速或者输出是复用了

【知青】哈尔滨Yamateh

复用是指什么呢 - -设置了变速时什么意思,ip核里应该没有这个选项吧

【知青】深圳-chenyh

复用指并转串

【知青】哈尔滨Yamateh

都没有啊 这些问题都没有吧

【知青】深圳-chenyh

变速指抽取,插值

【知青】哈尔滨Yamateh

没有啊 输入就是25K的采样频率 但是输出就不是 直接把数据接到AXI总线上的

【知青】深圳-chenyh

输出是多少K

【知青】哈尔滨Yamateh

12.5k左右

【知青】深圳-chenyh

那就是抽2了

【知青】哈尔滨Yamateh

不完全是12.5k啊, 而且抽取的话,输出也不是抽取的结果啊 感觉是有的控制信号没加好

求大神高见.....

|

| 共1条 1/1 1 |

Xilinx

Xilinx