|

版主: 51FPGA |

Zedboard I2C功能验证问题求助

[您是本帖的第1728位阅读者]|

zwj1234

最后登陆时间:2015-01-06 14:26:12 |

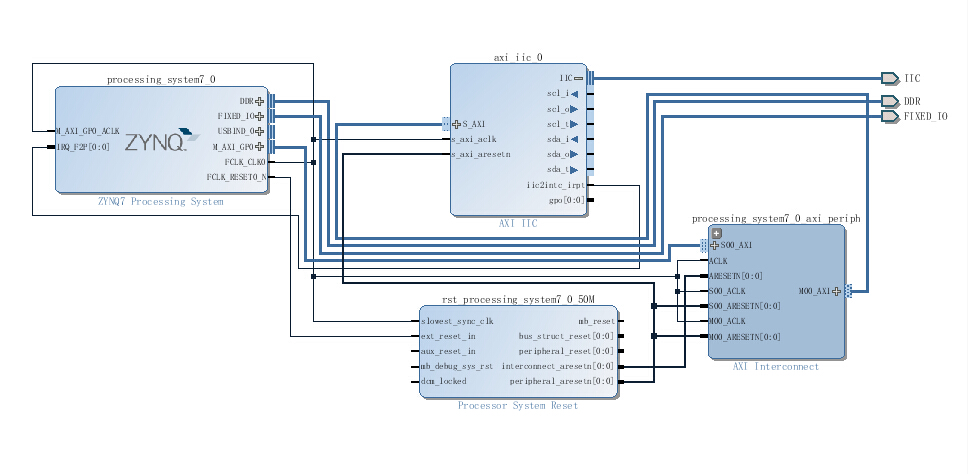

功能描述:使用上述硬件原理图,测试SCL和SDA信号产生的功能验证。 axi_iic_0为i2c控制器,是vivado自带的IP核;产生的SCL和SDA信号引到了zedboard开发板上,对应的pin为:SCL对应JA1,SDA对应JA2。

问题描述:使用上述硬件和下面的sdk代码进行测试,示波器上没有观测到信号变化。请求各位技术高手帮忙解决,非常感谢! 贴出sdk核心代码:(代码只是一部分比较重要的,整个工程需要创建BSP板级支持开发包)

int main(void)

XIic_Config *ConfigPtr; /* Pointer to configuration data */

/* Initialize the IIC driver so that it is ready to use.*/ ConfigPtr = XIic_LookupConfig(DeviceId); if (ConfigPtr == NULL) { return XST_FAILURE; } Status = XIic_CfgInitialize(&Iic, ConfigPtr, ConfigPtr->BaseAddress); if (Status != XST_SUCCESS) { return XST_FAILURE; } Status = XIic_Start(&Iic); if (Status != XST_SUCCESS) { return XST_FAILURE; } Status = XIic_SetAddress(&Iic, XII_ADDR_TO_SEND_TYPE, 0x50); //XII_ADDR_TO_SEND_TYPE宏定义 if (Status != XST_SUCCESS) { return XST_FAILURE; } //XIic_MasterSend(&Iic, WriteBuffer, 2); Status = XIic_Stop(&Iic); if (Status != XST_SUCCESS) { return XST_FAILURE; } return XST_SUCCESS; } 关键词:zedboard i2c控制器 AXI_IIC |

RE: Zedboard I2C功能验证问题求助

|

jobs

最后登陆时间:2015-01-28 22:16:26 |

Iic协议对引脚要求开漏输出,楼主通讯时要加上拉电阻。是不是这个原因啊?

|

我喜欢健身。 |

|

| 共2条 1/1 1 |

Xilinx

Xilinx