|

版主: 51FPGA |

关于fpga配置过程中的CRC校验的问题

[您是本帖的第2132位阅读者]|

xie0jing0

最后登陆时间:2014-11-14 00:56:50 |

请教各位,我用的是xilinx 的virtex2 FPGA,在测试中有这样一个问题:

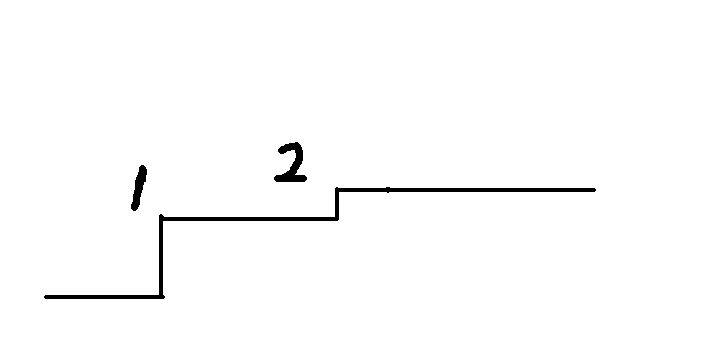

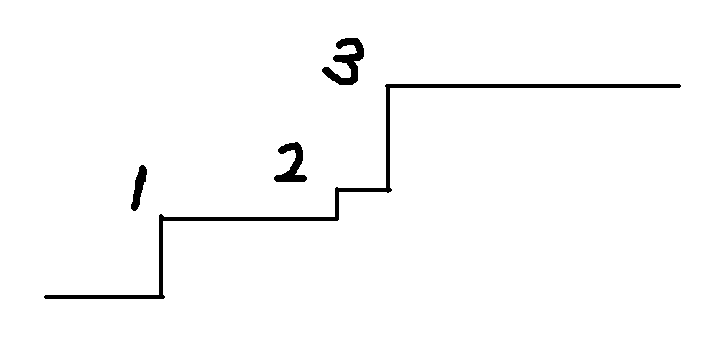

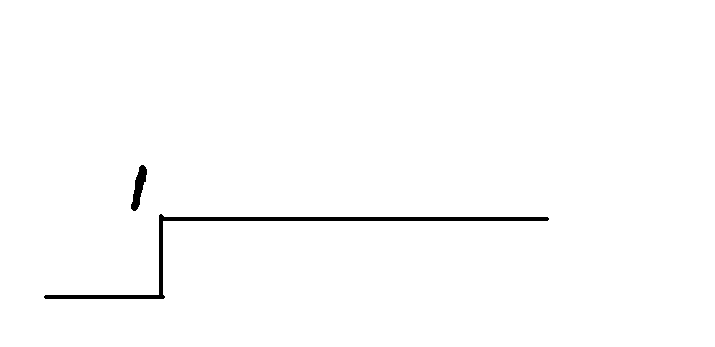

给FPGA烧写一个正常的MCS文件,断电重启后,对电流监测是这样的,FPGA正常工作。  当我把MCS文件中任意改变一行数以后,重新下载后,电流是这样的,FPGA也不工作。我人为是FPGA在配置过程中CRC校验没通过,所以终止了配置,此时配置芯片的INIT信号也被拉低了。  当我在ISE中产生MCS文件时,不勾选CRC校验,产生一个新的MCS文件,并也改动里面的内容,此时下载后有时FPGA可以配置成功,有时却不行,配置不成功时电流是这样子的,此时配置芯片的INIT信号也被拉低了:

通过测试DONE信号,1、2台阶应该是配置时间,3台阶应该是工作时间,那么请问第二个台阶是CRC校验的时间吗,为什么取消CRC校验有的MCS能配置成功,有时却不行? 在手册上看到CRC有两次,这种情况是第二次CRC没通过吗?两次CRC有什么不同呢? 盼望高人指点啊 关键词:配置 校验 |

|

此帖由xie0jing0于2014-04-01 00:29:03最后编辑

|

|

RE: 关于fpga配置过程中的CRC校验的问题

|

lianggui5

最后登陆时间:2015-01-26 19:27:26 |

帮顶,楼主问的问题很高深?不晓得楼主研究这个干什么?难道要反编译么

|

我行故我在。 |

|

RE: 关于fpga配置过程中的CRC校验的问题

|

lwukang

最后登陆时间:2014-11-03 22:51:35 |

你在生成的bit文件中,搜写CRC寄存器命令字段Ox3000_0001,看CRC值是不是填的默认值Ox0000_DEFC。一共两次CRC校验,你看两次是不是都屏蔽掉了。

|

RE: 关于fpga配置过程中的CRC校验的问题

|

lwukang

最后登陆时间:2014-11-03 22:51:35 |

对了,你不能直接改MCS文件,你只能改bit文件,bit文件才是你真正配置的内容,MCS文件是一个ASCII码文件,包含有有效数据的烧写地址,你用二进制编辑器打开MCS会发现每一行末尾都会有校验码存在Ox0D和Ox0A两个字节。楼主是想做动态刷新验证么?

|

RE: 关于fpga配置过程中的CRC校验的问题

|

Snake0301

最后登陆时间:2015-01-29 00:49:14 |

不懂,坐等大神现身说法。

|

学中取乐,书山有路先干为敬,学海无涯八宝做粥。。 |

|

RE: 关于fpga配置过程中的CRC校验的问题

|

xie0jing0

最后登陆时间:2014-11-14 00:56:50 |

lwukang的原帖 对了,你不能直接改MCS文件,你只能改bit文件,bit文件才是你真正配置的内容,MCS文件是一个ASCII码文件,包含有有效数据的烧写地址,你用二进制编辑器打开MCS会发现每一行末尾都会有校验码存在Ox0D和Ox0A两个字节。楼主是想做动态刷新验证么? 太感谢了,我再去试试。 是这样,我们有个板子会出现上电后程序没跑起来的情况,有时好,有时坏,检测电流就是和前面最后一幅图一样,所以想研究下是不是配置过程出问题了,就查到CRC了。 |

RE: 关于fpga配置过程中的CRC校验的问题

|

xie0jing0

最后登陆时间:2014-11-14 00:56:50 |

lwukang的原帖 对了,你不能直接改MCS文件,你只能改bit文件,bit文件才是你真正配置的内容,MCS文件是一个ASCII码文件,包含有有效数据的烧写地址,你用二进制编辑器打开MCS会发现每一行末尾都会有校验码存在Ox0D和Ox0A两个字节。楼主是想做动态刷新验证么? 再问一下请问有推荐的参考文献吗,谢谢啦 |

RE: 关于fpga配置过程中的CRC校验的问题

|

lwukang

最后登陆时间:2014-11-03 22:51:35 |

关于资料我都是看的Xilinx的文档,关于配置文件说明里面是有的。 上电加载不成功,有可能是电源峰值达不到导致,建议电源是否有设置限电流,或者把电流限小点看现象是不是出现更频繁。 加载不成功,你可以用示波器看看信号质量好不好,有可能是信号质量问题。 再如果你用主模式加载,主模式加载是用FPGA的时钟,这个时钟质量不是很好,工程应用不太推荐使用主模式加载。 |

RE: 关于fpga配置过程中的CRC校验的问题

|

xie0jing0

最后登陆时间:2014-11-14 00:56:50 |

lwukang的原帖 关于资料我都是看的Xilinx的文档,关于配置文件说明里面是有的。 上电加载不成功,有可能是电源峰值达不到导致,建议电源是否有设置限电流,或者把电流限小点看现象是不是出现更频繁。 加载不成功,你可以用示波器看看信号质量好不好,有可能是信号质量问题。 再如果你用主模式加载,主模式加载是用FPGA的时钟,这个时钟质量不是很好,工程应用不太推荐使用主模式加载。 受教了。电流也测了好多次,感觉没啥问题,负载能力也够。 再请教下如果INIT电平被拉低,就是因为CRC校验不过吧,不知还有别的原因吗, 另外autoCRC 与最后的CRC校验有区别吗,为啥要校验这么多次啊 |

RE: 关于fpga配置过程中的CRC校验的问题

|

lwukang

最后登陆时间:2014-11-03 22:51:35 |

CRC只会校验两次,上电你系统有个瞬态峰值电流,一般会很大 ,如果电源输出能力不够,是会出现FPGA加载不成功,换个好点电源试试。 加载过程中INIT拉低只会是CRC校验不过的原因,如果你能采到INIT下降沿且PROG为高的波形的话。 |

| 共10条 1/1 1 |

Xilinx

Xilinx