|

版主: 51FPGA |

Xilinx FIR输出数据截位的疑问

[您是本帖的第3825位阅读者]|

HisonicRisen

最后登陆时间:2013-09-24 11:36:07 |

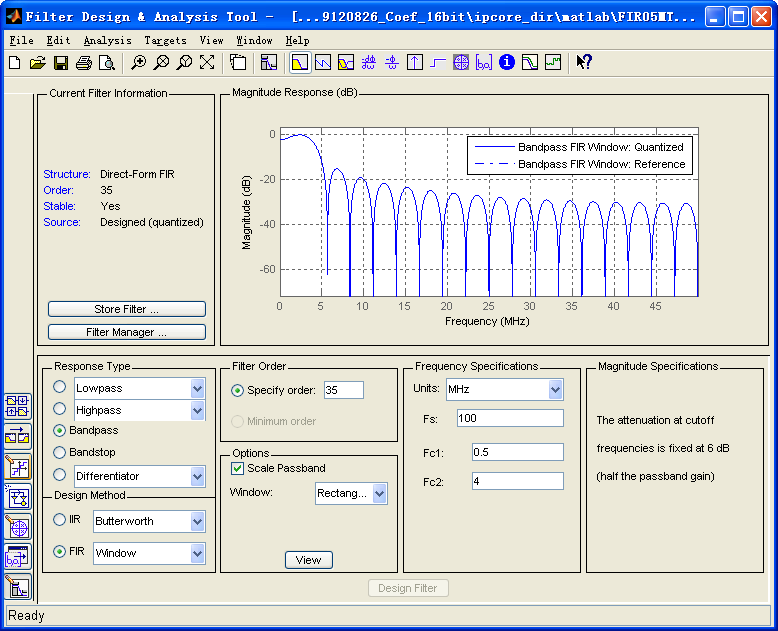

Hi,各位大侠,请教Xilinx FIR输出数据截位的问题: (1)用Fdatool设计一个0.5MHz - 4MHz的矩形FIR,通过COE文件导入FIR Compiler,35阶,系数16bit。如下图所示:

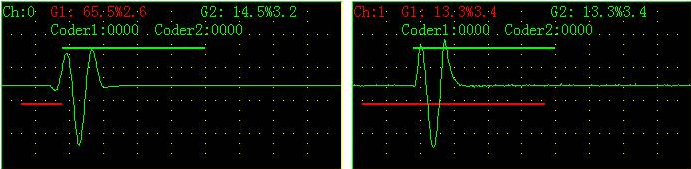

(2)AD是12bit,补码输入[-2048, 2047]。FIR Compiler输出数据dout为34bit。为了后续处理方便,想截取12bit。因此将所有系数求绝对值和,再乘以2048,得到最大输出值,落在31bit有符号数范围内。舍掉一个符号位,取dout[29:18],得到12bit滤波输出,进行显示。 (3)把通过滤波和不通过滤波器的数据画成,进行对比。 小信号输入时,没到AD量程,频带中心频率信号,滤波前后波高很接近。左图是通过滤波器输出数据波形,右图是不经过滤波的数据波形:

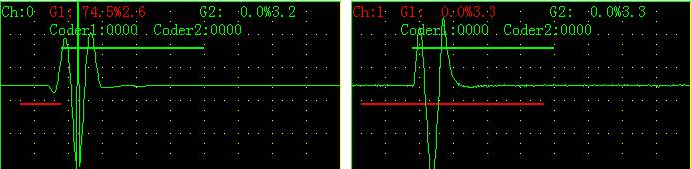

当增大输入信号时,滤波信号有异常,好像是溢出了:

(4)硬件设计的时候AD 12bit是offset binary输入的,通过将bit[11]取反得到two complement,然后FIR截取的12bit用同样的方法将补码转换为offset binary。 更换系数为1,0,0,0...,相当于不滤波,但是取FIR输出结果34bit的低12bit,即dout[11:0],显示没有问题。

各位大侠,给点建议。 关键词:Xilinx FIR |

RE: Xilinx FIR输出数据截位的疑问

|

HisonicRisen

最后登陆时间:2013-09-24 11:36:07 |

是不是和滤波器的系数增益有关系? 小数形式的系数,绝对值之和是1.3405。 |

RE: Xilinx FIR输出数据截位的疑问

|

zbtian

最后登陆时间:2013-10-14 10:41:29 |

想问下输出怎么截取啊,全精度的直接取低位么?还有算系数和什么的,有什么公式么 |

|

此帖由zbtian于2013-09-24 09:37:51最后编辑

|

|

RE: Xilinx FIR输出数据截位的疑问

|

HisonicRisen

最后登陆时间:2013-09-24 11:36:07 |

|

RE: Xilinx FIR输出数据截位的疑问

|

zbtian

最后登陆时间:2013-10-14 10:41:29 |

再问个问题,如果溢出了咋办?

|

| 共5条 1/1 1 |

Xilinx

Xilinx