|

版主: 51FPGA |

如何使用MIG3.6生成的example design

[您是本帖的第4731位阅读者]|

babydeer

最后登陆时间:2011-05-24 21:46:10 |

|

RE: 如何使用MIG3.6生成的example design

|

babydeer

最后登陆时间:2011-05-24 21:46:10 |

用的是ISE12.3的,里面自带的MIG。我用的是ISE自带的仿真器,把user design里面的仿真文件导入就能进行行为仿真,但导入example design里的仿真文件运行就会出这样的错:

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed user guide也看过了,里面就说把文件添加进去就行。。 你之前用的MIG2.1里面,example design和user design里面的东西有什么不同吗? |

RE: 如何使用MIG3.6生成的example design

|

babydeer

最后登陆时间:2011-05-24 21:46:10 |

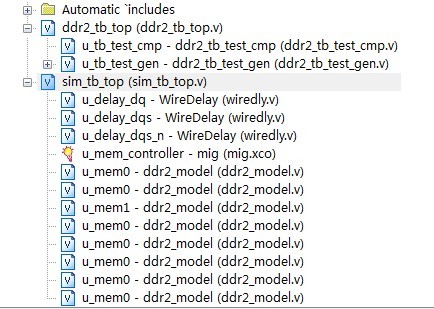

我把sim文件夹里的仿真文件都导进去了,如上面的图,也没有显示哪一个模块的缺失。把RTL文件夹里的也导入了还是不行。但user design里面的导入sim文件夹里的就可以。 |

| 共3条 1/1 1 |

Xilinx

Xilinx