|

版主: 51FPGA |

如何使用DPS(软件无线电开发套件)搭建FM收音机链路并完成业务演示

[您是本帖的第1871位阅读者]|

xuxuemingdw

最后登陆时间:2016-07-05 15:04:26 |

本帖就使用DPS搭建一个收音机链路,来为大家讲解如何开始一个链路的搭建。在开始搭建一个链路前,首先要做的是对链路原理的分析和仿真验证。

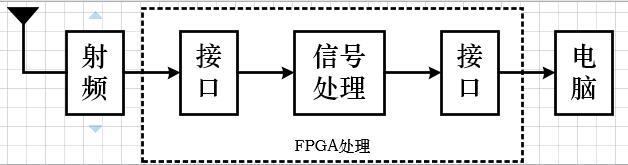

天线接收到信号后,经过射频板卡的处理,通过相应的接口将信号送至信号处理模块处理,最后再通过一些接口送至相应的信息终端播放。

这里我们需要弄明白的就是信号处理单元的流程:

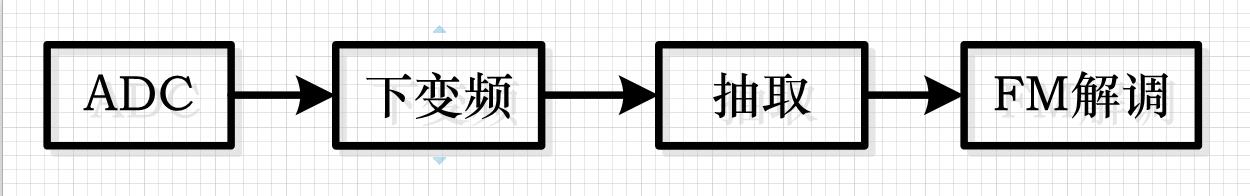

使用ADC将射频端送入的信号转换为数字信号,然后经过下变频,抽取滤波,FM解调输出的就是语音信号了。

二、参数仿真

看懂了算法原理,我们开始一个设计还需要对算法中的参数进行仿真验证:

仿真出需要的参数后,我们就可以开始搭建链路了。

对于原理的具体讲解,请查询各种资料吧,本帖就主要讲解收音机链路的搭建。

三、链路搭建

根据收音机原理图,我们知道,射频模块输出的信号,需要通过接口送至信号处理单元,所以,我们需要使用一个ADC板卡,将射频信号采集到FPGA中处理。

这里我们使用成都定为电子技术有限公司研发的FMC202射频板卡,他是一个输出零中频的2发2收的射频板卡,这里我们只需要使用它来接收一路信号即可,因此完全满足我们的需求。

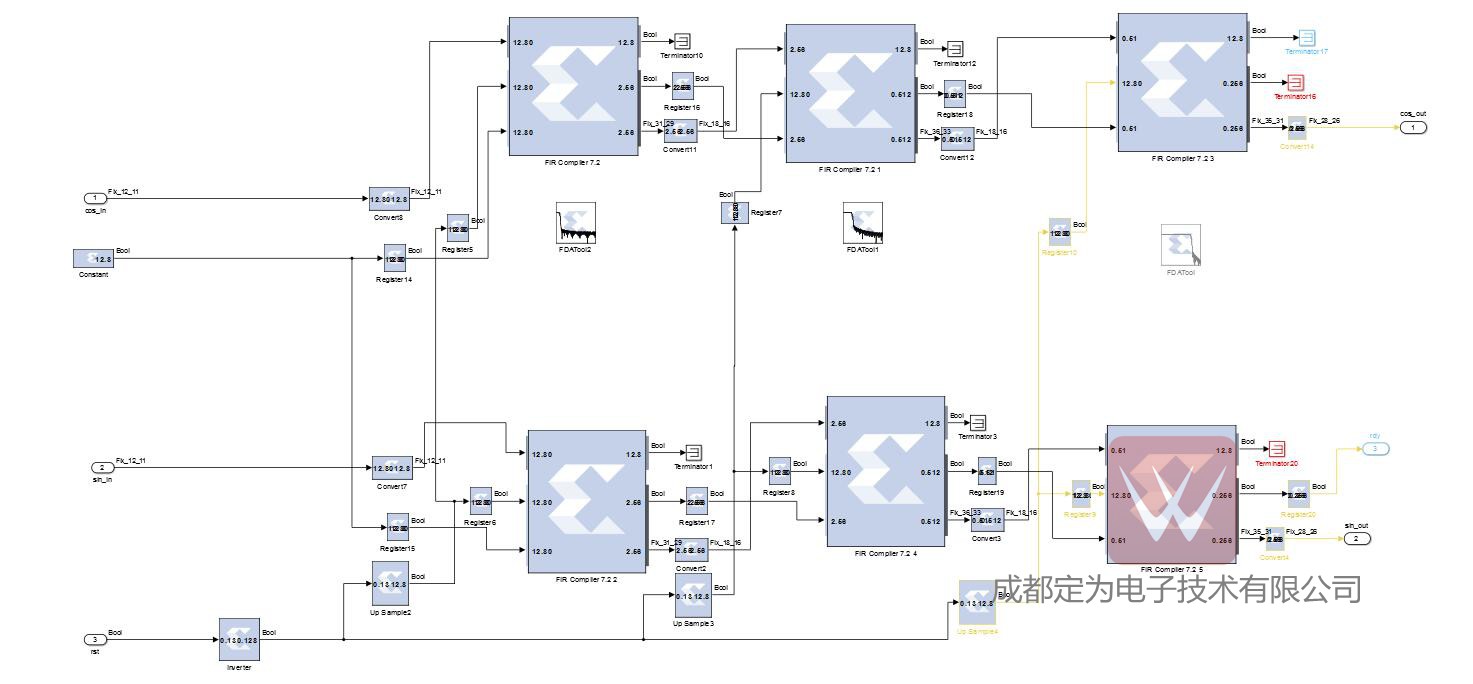

我先给出完整的收音机链路截图,后面再为大家详细讲解每个模块:

1、fmc202接口

FMC202为0中频射频板卡,硬件中集成了下变频至基带和滤波部分。因此,FMC202的RX输出为基带的I/Q信号,并且有2路IQ(因为是2发2收),这里我们只使用了FMC202的一个接收端,因此另一个接收端是空着的。这里我们设置FMC202基带信号的频率为12.8MHZ,也就是说从FMC202模块输出的数据的速率为12.8MHZ。

2、变频

根据收音机原理,我们应该先做的是变频,但是我们的FMC202射频板卡输出就是零中频信号,因此,就不需要我们再做变频操作。

3、抽取滤波

由于语音信号的频率在几十K级,所以,我们在这里需要做低通滤波以及抽取滤波,打开50_down_samples这个模块如下图:

可以看见,这里面总共有6个滤波器,上下两行滤波器分别对I、Q两路进行滤波

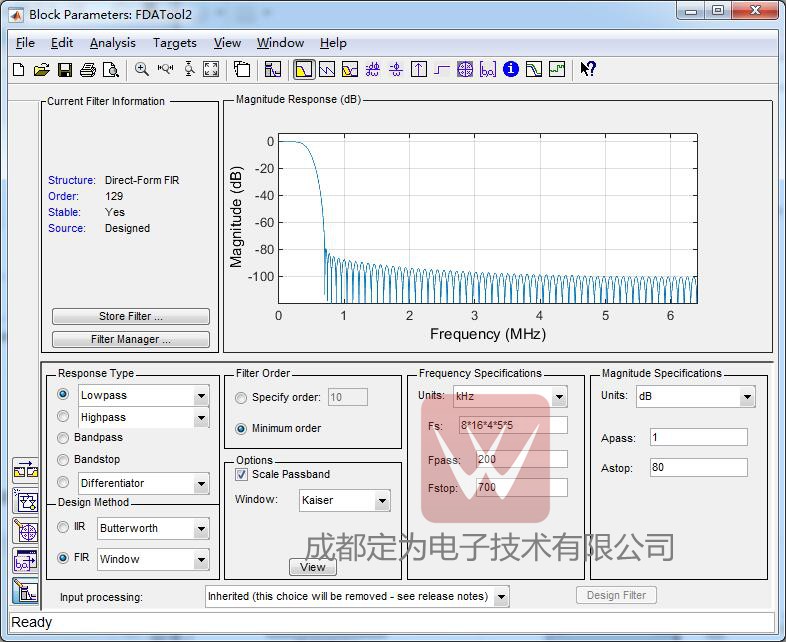

3.1、第一级抽取滤波器

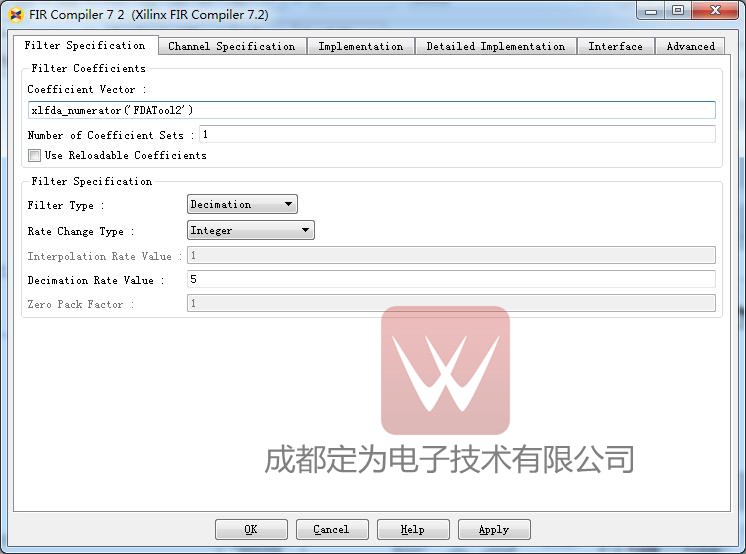

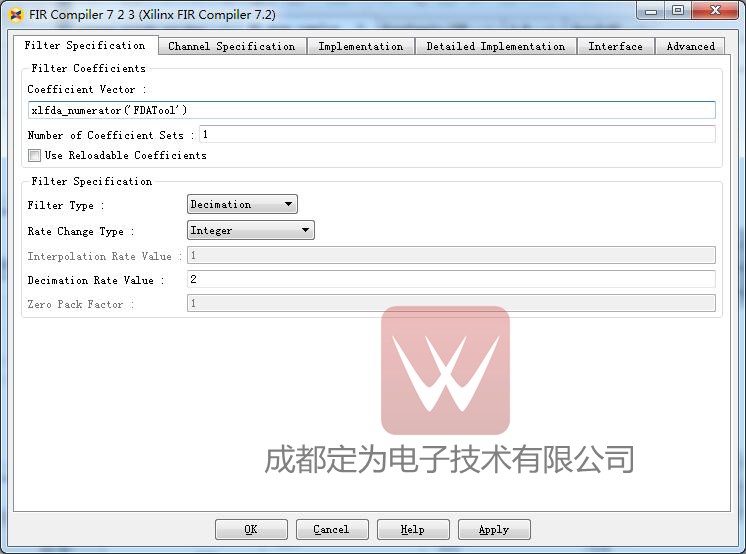

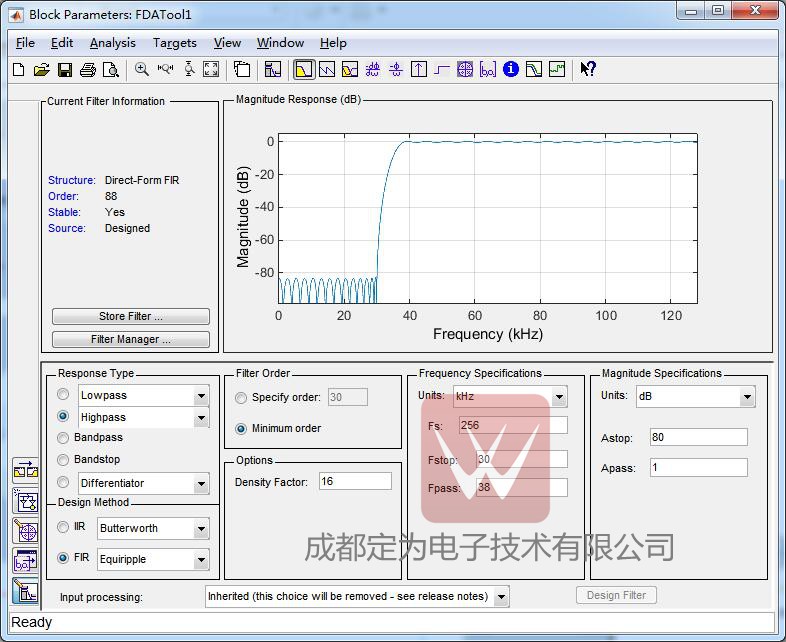

我们先看第一个滤波器,是一个截止频率为700K,带宽200K,5倍抽取的低通滤波器,其参数截图如下:

3.2、第二级抽取滤波器

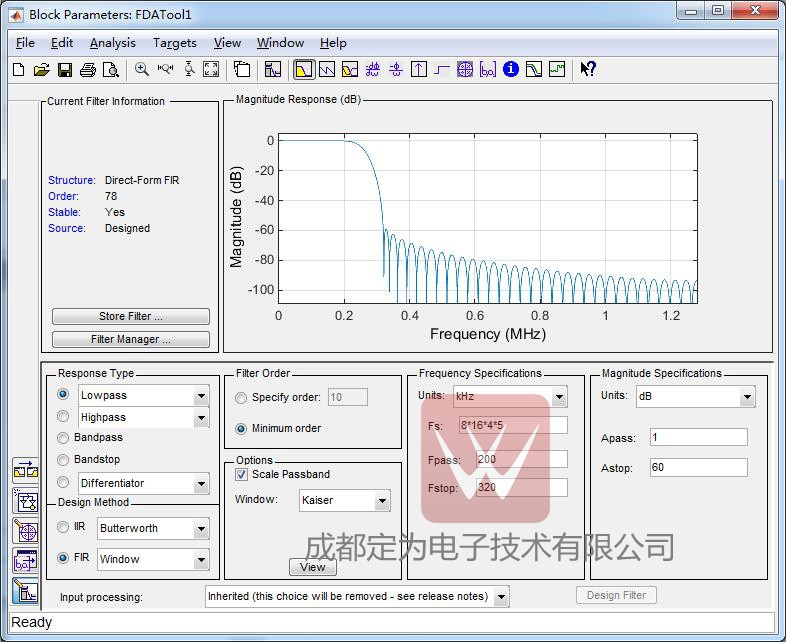

截止频率为320K,带宽为200K,5倍抽取的低通滤波器,其参数截图如下:

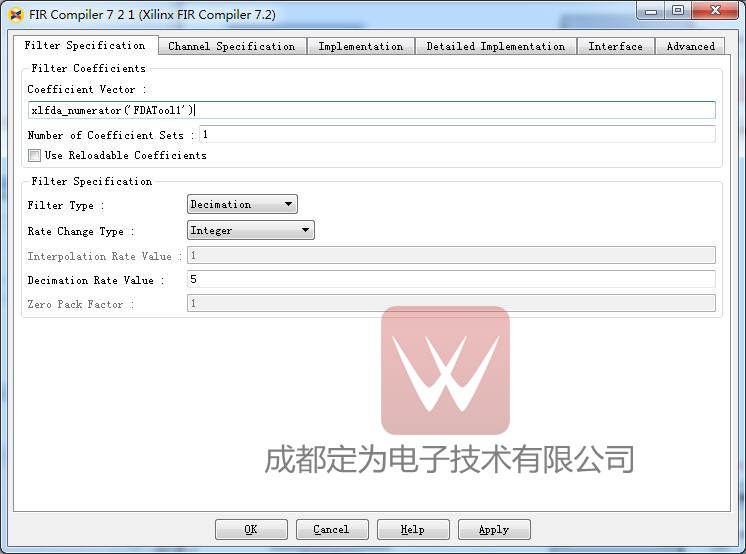

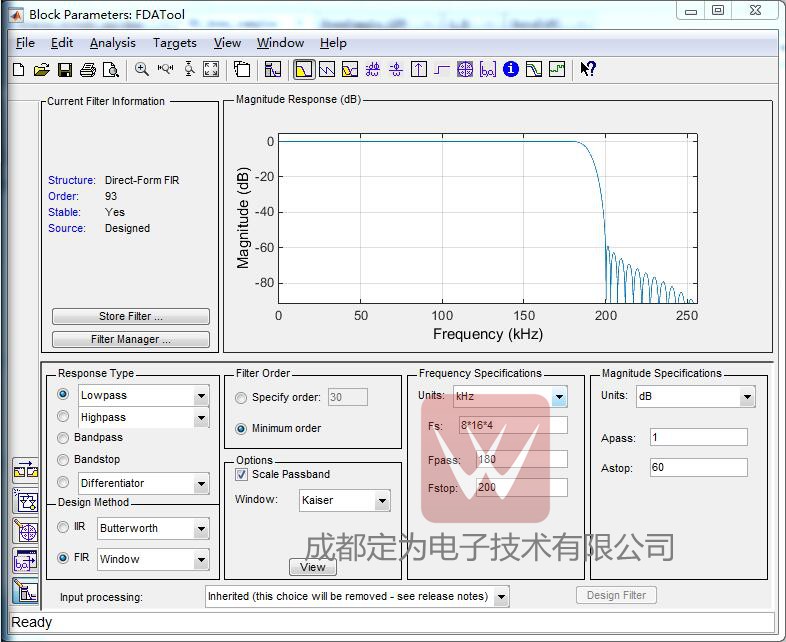

是一个截止频率为200K,带宽为180K,2倍抽取的低通滤波器,其参数截图如下:

3.4、论证

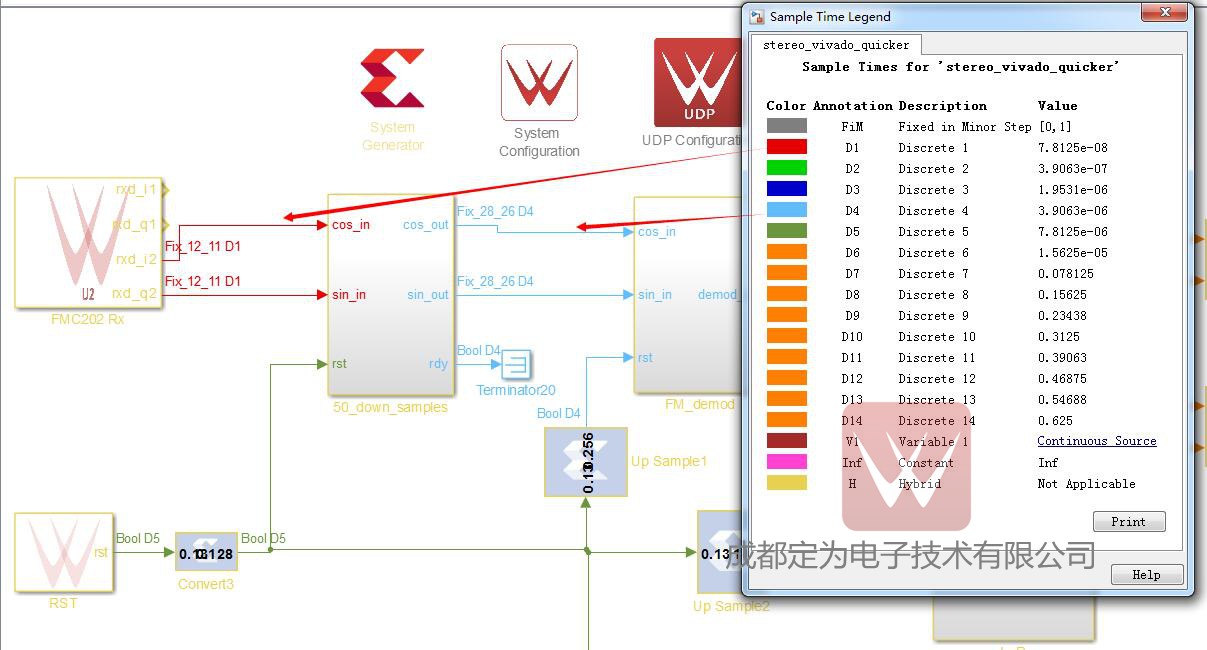

我们的信号速率从12.8MHZ变为12.8M/50=256K。我们从这里可以看出来:

可以发现,红色代表的速率为7.8125e-08S=1/7.8125e-08HZ=12.8MHZ,50_down_samples模块输出连线为淡蓝色代表的速率为3.9063e-06S=1/3.9063e-06HZ=256KHZ。256KHZ的采样速率已经完全足够语音信号的带宽。

4、fm解调

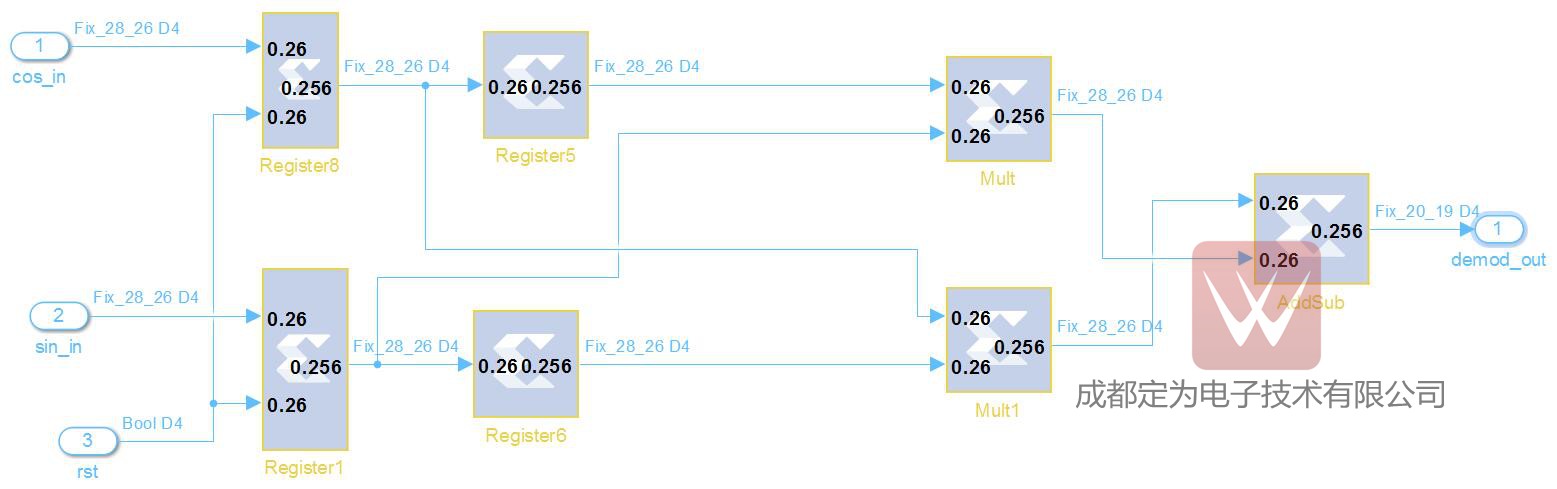

下面就开始对着256KHZ的语音信号进行FM解调,打开FM_demod模块:

实际就相当于求模运算。

5、声道划分

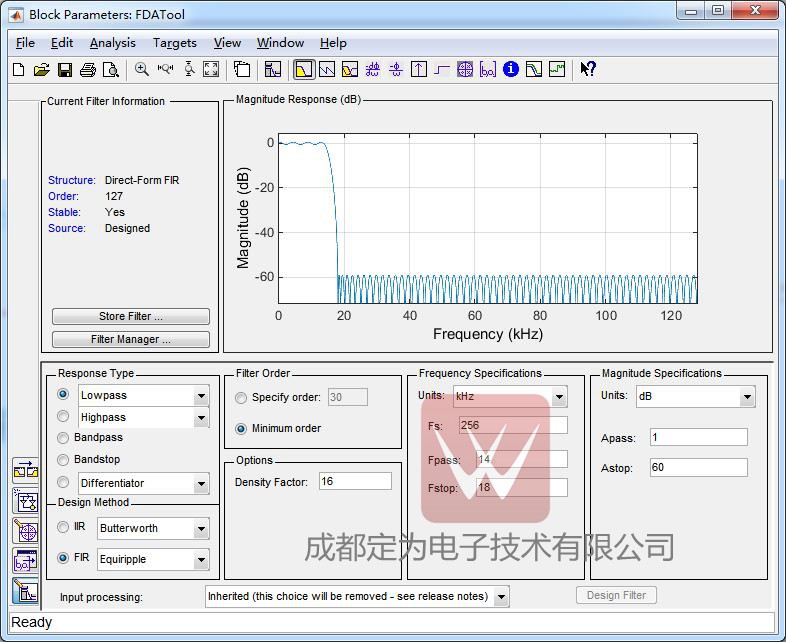

和信号部分DownSample_LPF模块的截图如下:

这是一个截止频率为18KHZ,带宽为14KHZ的低通滤波器,其参数设置截图:

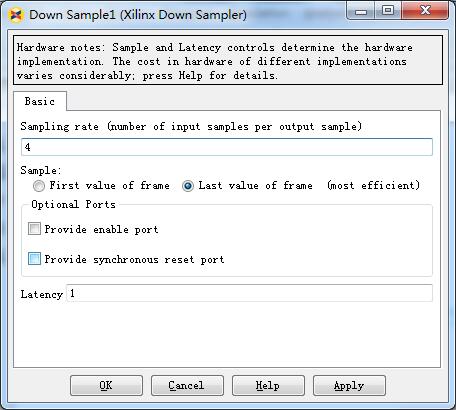

在上图中可以发现,滤波器输出有个Down Sample1模块,完成了数据速率的4倍下采样,其参数设置截图:

5.2、差信号部分

我们再看差信号的部分,L_R模块:

将语音信号经过一个滤波器后变频输出至后一个滤波器,我们先看第一个滤波器,其参数截图如下:

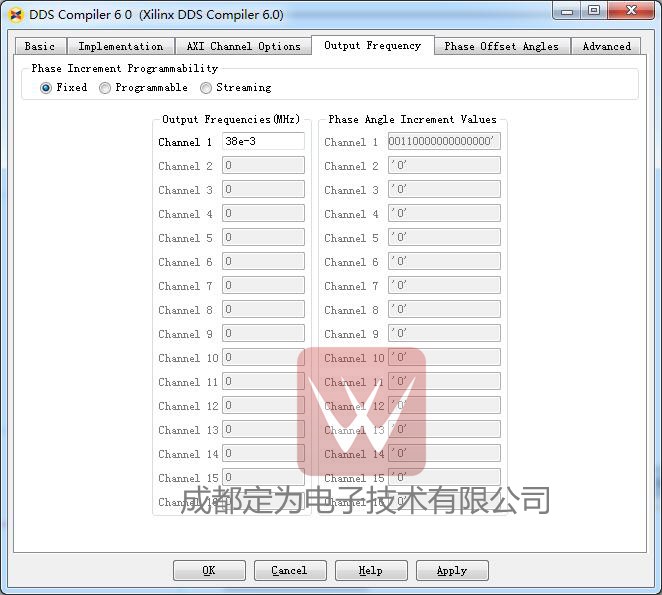

这个滤波器是一个截止频率为38KHZ,带宽为30KHZ的高通滤波器,这样就取出了语音信号的高音部分。下面是一个DDS模块,输出了一路正弦信号,其参数截图如下:

DDS的输出频率为38KHZ。将DDS输出的信号和高通滤波器输出的信号做乘法运算,也就说明,将滤波器输出的差信号部分的频率搬移到了基带。

然后将输出的信号经过低通滤波器和Down Sample1模块,把速率降为64K的信号,这部分和前边和信号部分一致,就不再讲述了。

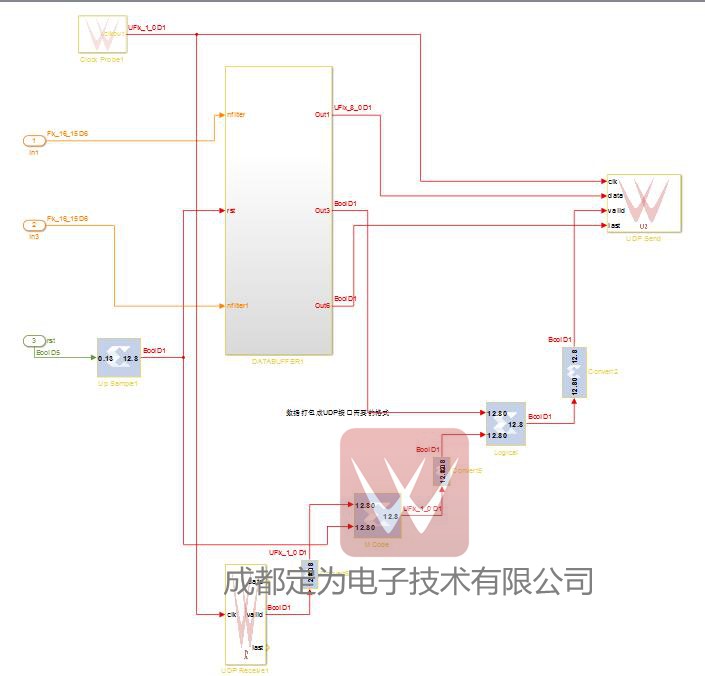

6、数据上传PC

最后,我们需要将这64K的左右两声道的信号传输到PC上来播放,模块DataToPC的截图如下:

7、生成bit

这里面就完成将输入的语音信号通过UDP接口上传至PC端来实时播放,里面使用了FIFO缓存数据,当数据达到了一个UDP数据包的长度后,就输出至UDP接口,用户只需要使输入UDP端口的数据满足该协议即可。具体操作就不再讲述。

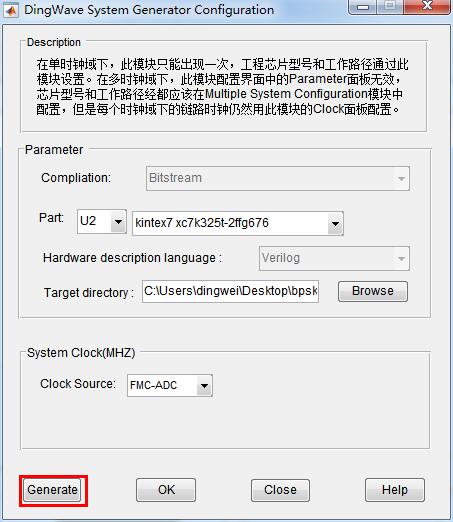

搭建好链路后,我们开始生成bit文件,如下图所示:

设置好生成bit的路径和芯片信号,由于我们使用了FMC202板卡,为了保证数据和时钟对齐,我们使用ADC时钟,即FMC202板卡上的ADC的时钟。点击Generate生成bit。我们的示例中有一个生成给U2的bit。

四、bit下载与配置

1、bit下载与射频配置

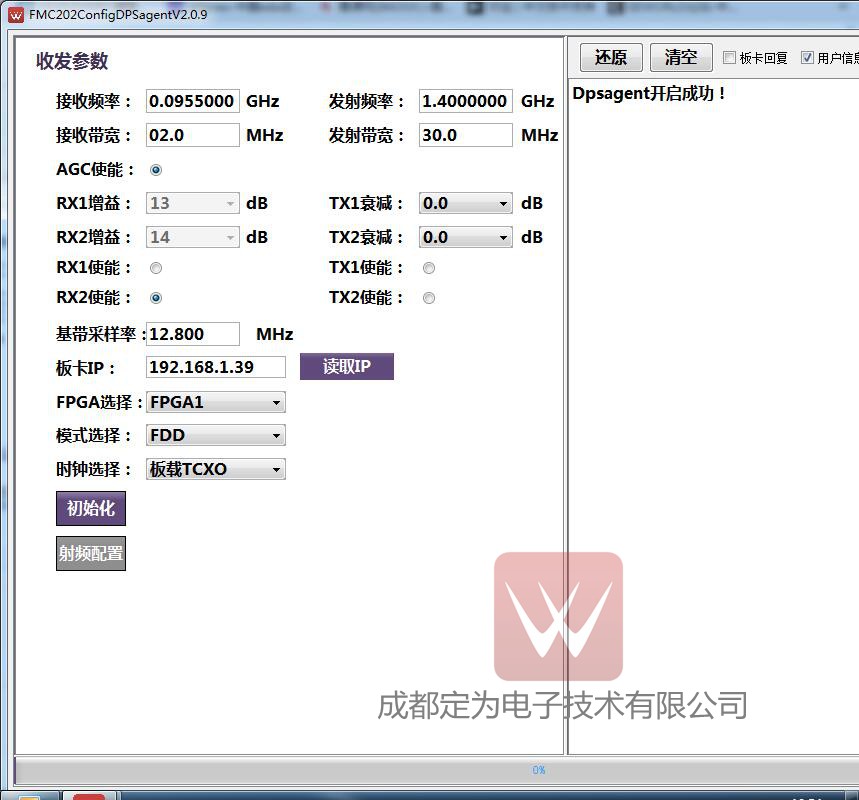

生成bit后,准备好硬件平台,连接好天线,加载bit至所生成的板卡中,然后开始配置FMC202的射频频点,打开FMC202的配置界面,如下如所示:

这里的接收频点,可以根据当地的广播信号频率来设置,截图中设置的是95.5M,接收带宽设置为2M,开启AGC使能,只使用了FMC202的接收2通道,所以,我们只选择RX2使能。这里的基带采样率就是我们链路中FMC202 RX模块上设置的那个速率。设置好IP和FPGA后,即可点击初始化->配置,如果配置失败,请确认bit文件是否下载正确,或者重新配置。

2、业务传输

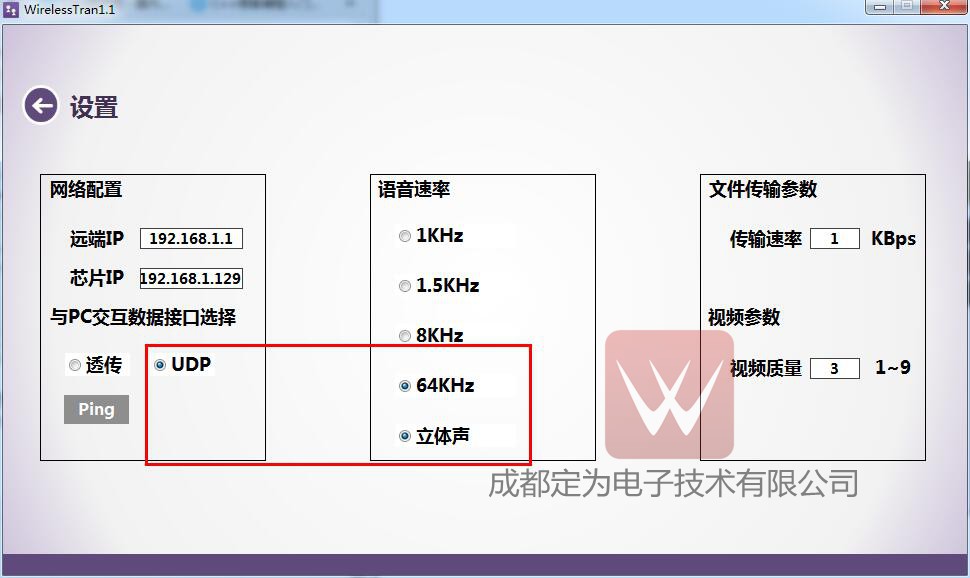

在DPS的业务传输界面里,点击设置,由于我们的链路中DataToPC模块里面使用的是UDP传输方式,所以在设置里面选择UDP,我们的语音速率为64KHZ,左右声道,因此选择语音速率为64KHZ,立体声。截图如下:

设置好了以后,点击返回->电台通信->接收,即可听见你所配置的广播信号,如果听见的效果不好,可以试着移动天线的位置。

安装新版DPS2.0软件后,即可打开附件中的链路,附件中bit支持U2平台的xc7k325t-2ffg676芯片,用户可以直接下载。

关键词:无线通信 软件无线电 收音机链路 DPS Vava |

| 共1条 1/1 1 |

Xilinx

Xilinx