|

版主: 51FPGA |

大家来帮忙分析下这个串并转换,很神奇啊,理解不上去了

[您是本帖的第2242位阅读者]|

fenglema

最后登陆时间:2014-06-22 22:43:41 |

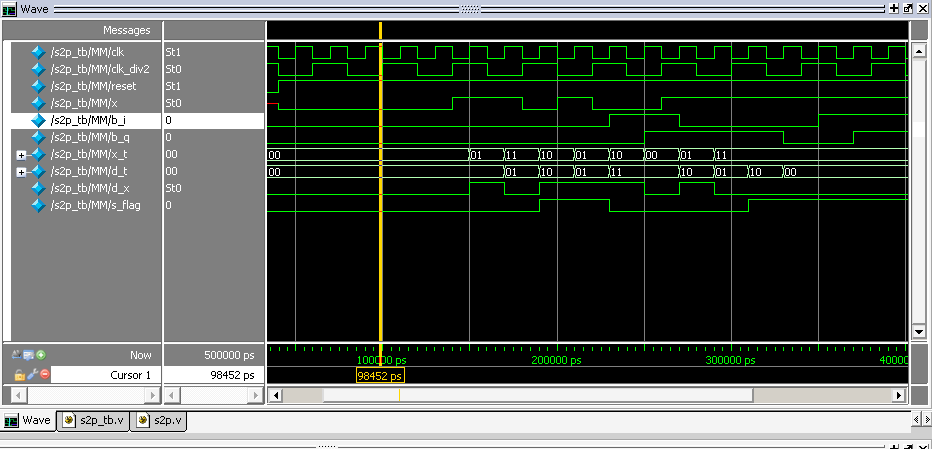

`timescale 1ns / 1ps reg b_i, b_q; // 完成差分预编码, d_x(n) = x(n)*x(n-1),等效于求异或 // 产生分流的I、Q信号 关键词:大家 帮忙 分析 这个 转换 神奇 理解 不上 去 |

疯了吗。 |

|

RE: 大家来帮忙分析下这个串并转换,很神奇啊,理解不上去了

|

fenglema

最后登陆时间:2014-06-22 22:43:41 |

d_x值多敲了一个0……应该是0000 0100 1110 1 吧。。失误了,没有再次编辑界面?

|

疯了吗。 |

|

RE: 大家来帮忙分析下这个串并转换,很神奇啊,理解不上去了

|

larrybird

最后登陆时间:2014-10-29 15:16:14 |

大学的时候学的是VHDL,有点不明白

|

hai。 |

|

RE: 大家来帮忙分析下这个串并转换,很神奇啊,理解不上去了

|

fenglema

最后登陆时间:2014-06-22 22:43:41 |

没有人来啊,看来这个论坛也要倒闭了

|

疯了吗。 |

|

RE: 大家来帮忙分析下这个串并转换,很神奇啊,理解不上去了

|

fenglema

最后登陆时间:2014-06-22 22:43:41 |

今天一看,这个问题终于突然明白了。代码中0代表1,1代表-1。然后根据msk调制的原理顺理成章可推出IQ两路信号是:I路001001;Q路是001101.怎么和书上的以及上面的不一样呢?别着急,IQ两路信号占用的是2Tb,所以0对应2个00,1对应2个11.这回对了吧,呵呵。有不懂得可以留言。 |

疯了吗。 |

|

RE: 大家来帮忙分析下这个串并转换,很神奇啊,理解不上去了

|

fenglema

最后登陆时间:2014-06-22 22:43:41 |

另外,注意这个串并转换可不是一般意义的串并转换。是msk调制原理对应的变换,是一种特殊算法

|

疯了吗。 |

|

| 共6条 1/1 1 |

Xilinx

Xilinx