|

版主: 51FPGA |

基于TimeQuest Timing Analyzer

[您是本帖的第1183位阅读者]|

jollylin

最后登陆时间:2012-01-30 16:09:13 |

基于TimeQuest Timing Analyzer

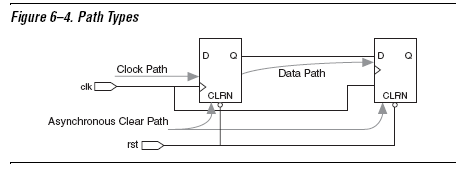

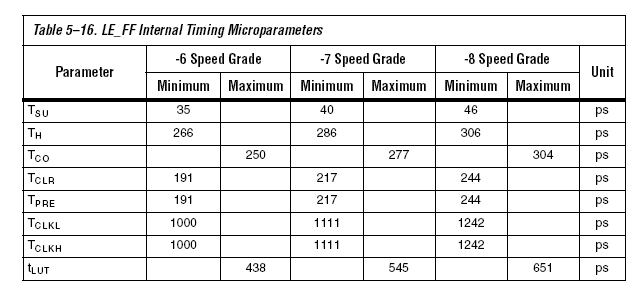

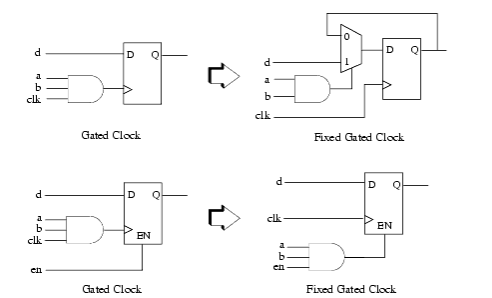

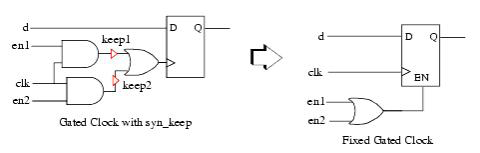

一、 基础篇: 常用的约束(Assignment/Constraints)分类:时序约束、区域与位置约束和其他约束。 主要用途: 1、时序约束: 规范设计的时序行为,表达设计者期望满足的时序条件,指导综合和布局不同阶段 的优化算法等。简而言之就是规范和指导的作用。倘若合适的话,它在综合、影射、布 局布线的整个流程中都会起指导作用,综合器,布线器都会按照你的约束尽量去努力实 现,并在静态时序分析报告中给出结果。 2、区域与位置约束: 指定芯片I/O 引脚位置以及指导实现工具在芯片中特定的物理区域进行布局布线。 3、其他约束: 主要作用: 1、提高设计的工作频率: 通过附加时序约束可以控制逻辑的综合、映射、布局和布线,以减少逻辑和布线的 延时。其实,综合后的结果只是给出你的设计一个大概的速度范围,布线后的速度比综 合后给出的结果要低,这是因为综合后只有器件的延时,而布线后除了器件的延时还要 加上布线上的延时。至于低多少就看设计者的约束能不能很好的指导布线器进行优化 了。 2、获得正确的时序分析报告: 在QuartusII 中,内嵌的是静态时序分析工具(STA, Static Timing Analysis),他的 作用就是设计进行评估,只有在正确的输入时序约束的情况下,才能得到可靠的报告。 同时也是做FPGA 设计时是必须的一个步骤,事实上大家一般都已经做了这一步,我们 在FPGA 加约束、综合、布局布线后,会生成时序分析报告,设计人员会检查时序报告、 根据工具的提示找出不满足setup/hold time 的路径,以及不符合约束的路径,这个过 程就是STA。 此外,STA 是相对于动态时序仿真而言的,它通过对每个时序路径的延时分析,计 算出最高的设计频率(fmax),发现时序违规(Timing Violation)。注意:静态时序分 析仅仅聚焦于设计时序性能的分析,而不会涉及逻辑性能。 在 STA中主要分析的路径有:时钟路径,异步路径,数据路径。  附加时序约束需要注意的几点: 1、加时序约束要完整,因为STA 根据时序约束做检查,如果约束不正确,ST 结果就不准确.经常会出现功能验证正确而后仿真结果不正确的问题,一般是由setup time/hold time不满足等时序问题引起的,说明在综合与布局布线过程中没有进行 约束或者约束条件不完全,导致STA 分析结果不准确、不完全。 2、除了全局约束外,尽量不要加局部约束。 3、综合的结果和布局布线的结果不是正比的关系。综合约束太高,可能布局布线反而 布不上去,综合约束低一点,有时候布线结果可能更高。 4、倘若约束加的过细,留给工具的空间就会很小了,满足了你的局部约束,其他地方 可能就可能满足不了,而这个也和资源利用率有关系,如果资源用得太多,又加了 很多的约束,很可能就会实现失败,如果只是用了很少的资源,相对就会好一些。 名字解释: 1. Clock Setup Time(tsu,输入建立时间): 时钟有效沿到达前,数据和使能信号已 经准备好的最小时间间隔。此外,存在utsu,指的是触发器内部的固有建立时间, 不能改变。一般会给出其最小值,单位:ps,如下图所示为‘cycloneII’内部逻辑 单元的时序参数。 2. Clock Hold Time(th,输入保持时间):保证有效时钟沿正确采样的数据和使能信号 在时钟沿之后的最小稳定时间。此外,存在uth,指是寄存器内部固有的保持时间, 一般会给出最小值。 3. Clock to Output Delay(tco,时钟输出延时):时钟有效沿到数据有效沿的最大间隔。 同样存在utco 表示将数据送到输出端口的内部延时参数,一般区最大值。 4. tpd:管脚到管脚的输出延时。 5. Slack:表示设计是否满足时序的一个标准,正的表示满足时序要求,负的就表示 不满足,以红字示出。对于不同的检查对象,计算公式均有不同,下篇会详细说明。 6. 时钟偏斜(Clock Skew),指一个同源时钟到达两个不同的寄存器时钟端的时间差 别。主要原因:两条时钟路径到达同步远见的长度不同,避免方法之一就是采用全 局时钟网络。  7、launch edge:前级逻辑单元馈送数据的时钟有效沿。 8、latch edge:后级逻辑单元捕获、锁存数据的时钟有效沿。  9、recovery time:是指在时钟有效沿到来之前,异步控制信号保持稳定的最短时间。 计算方式类似于setup time,主要用于对异步路径的分析。 10、removal time:是指在时钟有效沿到来之后,异步控制信号保持稳定的最短时间。 计算方式类似于Hold time,主要用于对异步路径的分析。 与 Synpify 相关的设计优化方法: 门控时钟的优化: 在 FPGA 设计中,存在一些特有的low-skew的时钟网络,但是倘若在FPGA的一 些布线资源内,存在大量的自定义时钟树(clk-tree),就会引起门控时钟的出现,而门 控时钟会引起严重的时钟歪斜和时序问题。 如果采用FPGA内部的全局时钟网络,用户就可以节省有限的布线资源,同时加快 布局的效率。由此可知,最好的解决办法就是分离时钟输入端的门逻辑,并将自定义的 用户时钟树融合到全局时钟树上。Synplify 就可以很好地解决这个问题:它采用的方法 是: l Inserting a multiplexer in front of the input pin of the synchronous element and connecting the clock net directly to the clock pin l Moving the gating from the clock input pin to the dedicated enable pin, when this pin is available. 简而言之,就是1搬移组合逻辑到输入端或使能端,2同时将时钟网络直接接到时 钟输入上。   关键词:基于 TimeQuest Timing Analy |

jolly。 |

|

| 共1条 1/1 1 |

Xilinx

Xilinx